13-12 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.8 Transmit/Receive Control Register (TXRXCTRL)

Communications between the debug handler and debugger are controlled through handshaking bits

that ensures the debugger and debug handler make synchronized accesses to TX and RX. The

debugger side of the handshaking is accessed through the DBGTX (Section 13.11.4, DBGTX

JTAG Register) and DBGRX (Section 13.11.6, DBGRX JTAG Register) JTAG Data Registers,

depending on the direction of the data transfer.The debug handler uses separate handshaking bits in

TXRXCTRL register for accessing TX and RX.

The TXRXCTRL register also contains two other bits that support high-speed download. One bit

indicates an overflow condition that occurs when the debugger attempts to write the RX register

before the debug handler has read the previous data written to RX. The other bit is used by the

debug handler as a branch flag during high-speed download.

All of the bits in the TXRXCTRL register are placed such that they can be read directly into the CC

flags in the CPSR with an MRC (with Rd = PC). The subsequent instruction can then conditionally

execute based on the updated CC value

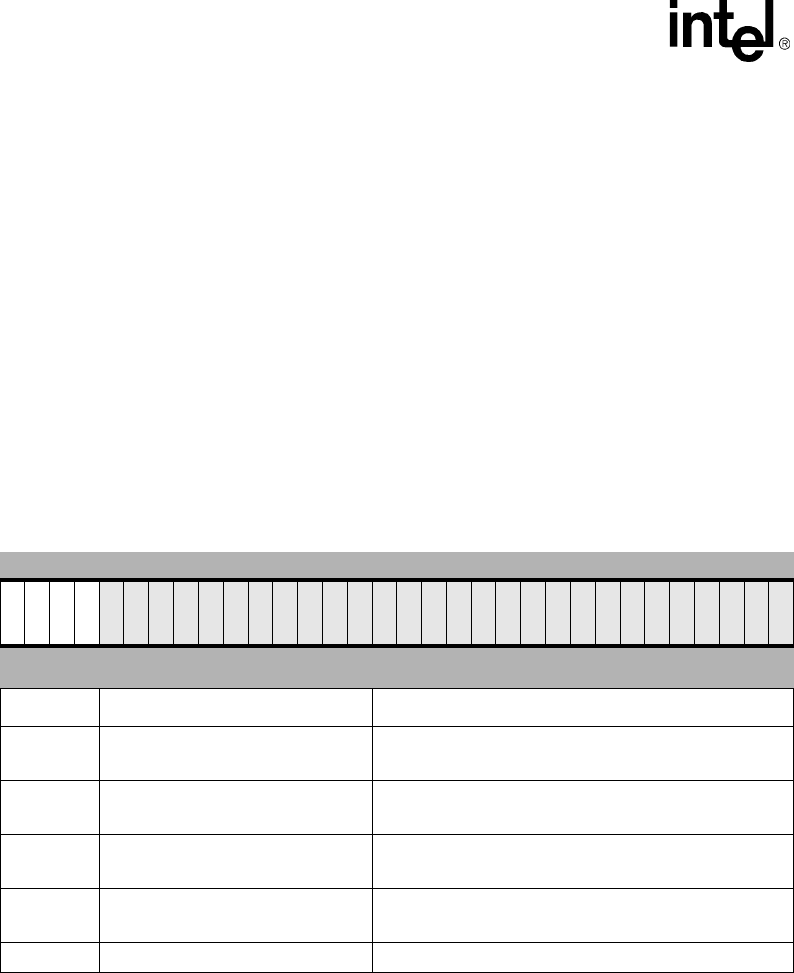

Table 13-6. TX RX Control Register (TXRXCTRL)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

R

O

V

D

T

R

reset value: 0x00000000

Bits Access Description

31

SW Read-only / Write-ignored

JTAG Write-only

RR

RX Register Ready

30 SW Read / Write

OV

RX overflow sticky flag

29

SW Read-only/ Write-ignored

JTAG Write-only

D

High-speed download flag

28

SW Read-only/ Write-ignored

JTAG Write-only

TR

TX Register Ready

27:0 Read-as-Zero / Write-ignored Reserved