Developer’s Manual March, 2003 8-5

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

System Management

8.3 Power Management

The Intel

®

80200 processor provides low power modes: idle and sleep, which are listed in

increasing power saving order. Table 8-3 describes the attributes of each low power mode.

8.3.1 Invocation

The Intel

®

80200 processor provides a simple instruction to enter into low power mode. See

Table 7-24, “Clock and Power Management” on page 7-21 for exact commands. This instruction

waits for all processing to complete, asserts the PWRSTATUS output pins and waits for a wake up

event to transition back into the normal running mode. For idle, the wake-up event is the assertion

of FIQ# or IRQ# pins. If the interrupt is masked, the Intel

®

80200 processor still wakes-up but

won’t service the interrupt.

The only way to exit Sleep mode is to go through the reset sequence. Sleep mode provides the

greatest power savings since the Intel

®

80200 processor supply voltage can be reduced to zero.

8.3.2 Signals Associated with Power Management

PWRSTATUS[1:0] is a 2-bit output from the Intel

®

80200 processor. It carries information about

the current power mode on the part. Table 8-4 shows the encoding of the PWRSTATUS[1:0]

signals.

The external interrupt pins may be used to exit Idle mode. If MCLK is toggling, asserting FIQ# or

IRQ# wakes the Intel

®

80200 processor up, even if the interrupt is disabled.

If interrupts are enabled, it takes some time after the processor is woken up. The exact timing

depends on the CCLK:MCLK ratio and implementation details, and can not be reliably predicted.

If software needs to guarantee it does not proceed until an interrupt is taken, it should poll for an

asserted interrupt after it is woken up.

As with all external interrupts, the interrupt source must keep the wake-up interrupt asserted until

told otherwise by software running on the Intel

®

80200 processor. See Chapter 9, “Interrupts”, for

more information. After an interrupt is asserted, the Intel

®

80200 processor takes approximately

10 CLK cycles to exit Idle mode.

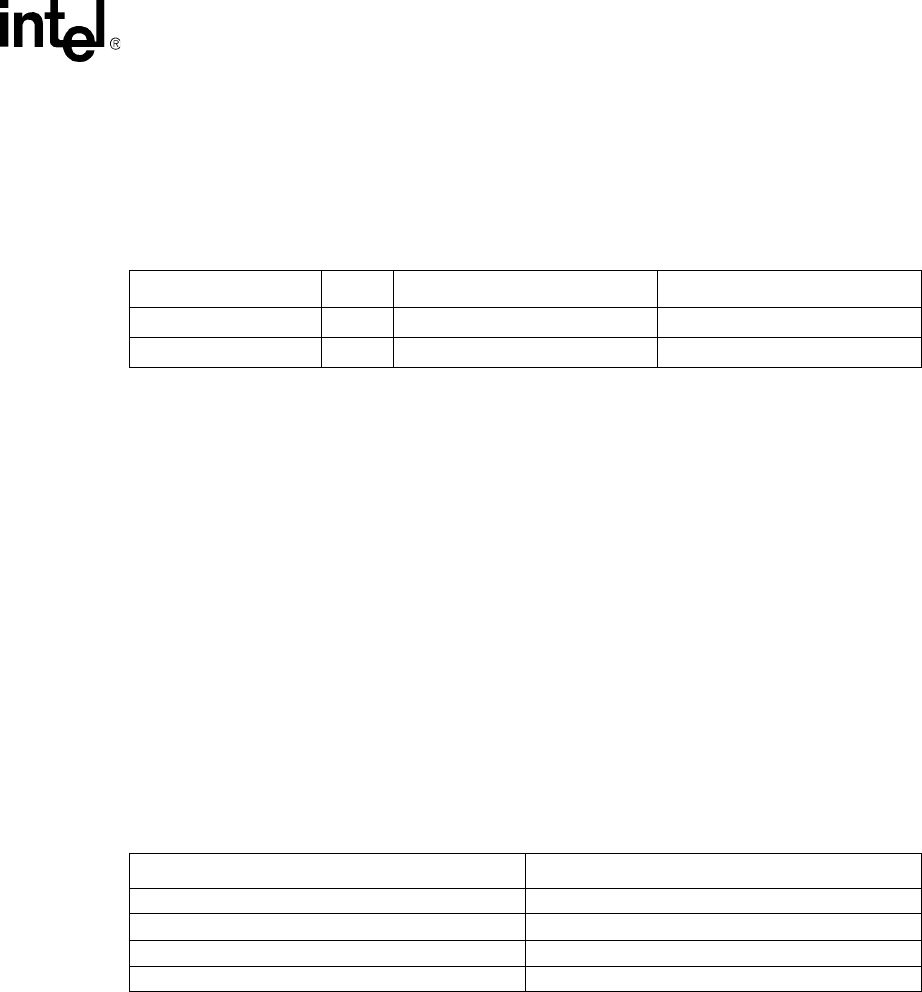

Table 8-3. Low Power Modes

Low Power Mode PLL Architectural State Wakeup Method

Idle On Retained FIQ#/IRQ#

Sleep Off Must be saved prior to entering RESET#

Table 8-4. PWRSTATUS[1:0] Encoding

PWRSTATUS[1:0] Power Mode

00 Normal

01 Idle

10 Reserved

11 Sleep