Developer’s Manual March, 2003 11-9

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Bus Controller

11.4.2 ECC Error Registers

The contents of these registers should only be considered valid if the corresponding bit in register

BCUCTL is set. When an error is detected, the BCU selects a free ELOGx/ECARx register pair

and updates it with information relevant to the error. It then sets BCUCTL.Ex.

ECARx holds the physical address associated with the transaction that caused the error. If the

transaction was a multiple-cycle burst, then only the initial address is captured, the actual error

occurred at some point during the burst. Because a burst can cover up to 32 bytes, software may

only know that the error was in a range: ECARx .. ECARx + 31.

System software bears the burden of translating this address to a logical one, if needed. Since

changes to the page tables may make this a non-trivial exercise, systems that respond to errors may

wish to delay page table updates until the BCU is quiescent (as determined by the BCUCTL.TP

bit).

For ECC errors, the lower bits of this register are always zero, because ECC always operates on

64-bit items. This means, ECC errors have an ECARx register in which bits 2..0 is zero.

For bus aborts, which could occur on byte-sized transactions, all address bits are recorded.

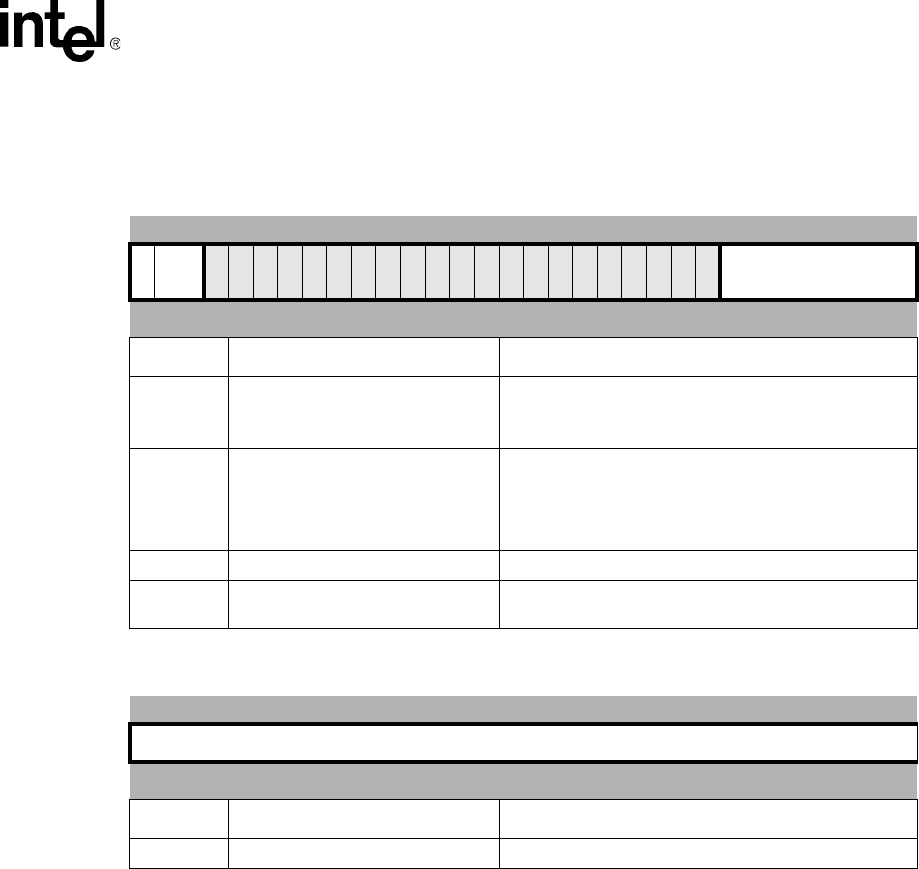

Table 11-4. ELOG0, ELOG1(Registers 4, 5)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

W

ET syn

reset value: undefined

Bits Access Description

31 Read / Write-ignored

RW - indicates the direction of the errant transfer

0 = read error

1 = write error

30:29 Read / Write-ignored

ET - Error Type

00 = single bit ECC error

01 = multi-bit ECC error

10 = bus abort

11 = reserved

28:8 Read-unpredictable / Write-as-0 reserved

7:0 Read / Write-ignored

syn - the syndrome value that indicated the error. This

field has an undefined value if ET is greater than 1.

Table 11-5. ECAR0, ECAR1(Registers 6, 7)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

addr

reset value: undefined

Bits Access Description

31:0 Read / Write-ignored addr - the physical address that yielded an error