Developer’s Manual March, 2003 13-41

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.14.4.2 Loading IC During a Warm Reset for Debug

Loading the instruction cache during a warm reset may be a slightly different situation than during

a cold reset. For a warm reset, the main issue is whether the instruction cache gets invalidated by

the processor reset or not. There are several possible scenarios:

• While reset is asserted, TRST# is also asserted.

In this case the instruction cache is invalidated, so the actions taken to download code are

identical to those described in Section 13.14.4.1

• When reset is asserted, TRST# is not asserted, but the processor is not in Halt Mode.

In this case, the instruction cache is also invalidated, so the actions are the same as described in

Section 13.14.4.1, after the LDIC instruction is loaded into the JTAG IR.

• When reset is asserted, TRST# is not asserted, and the processor is in Halt Mode.

In this last scenario, the mini instruction cache does not get invalidated by reset, since the

processor is in Halt Mode. This scenario is described in more detail in this section.

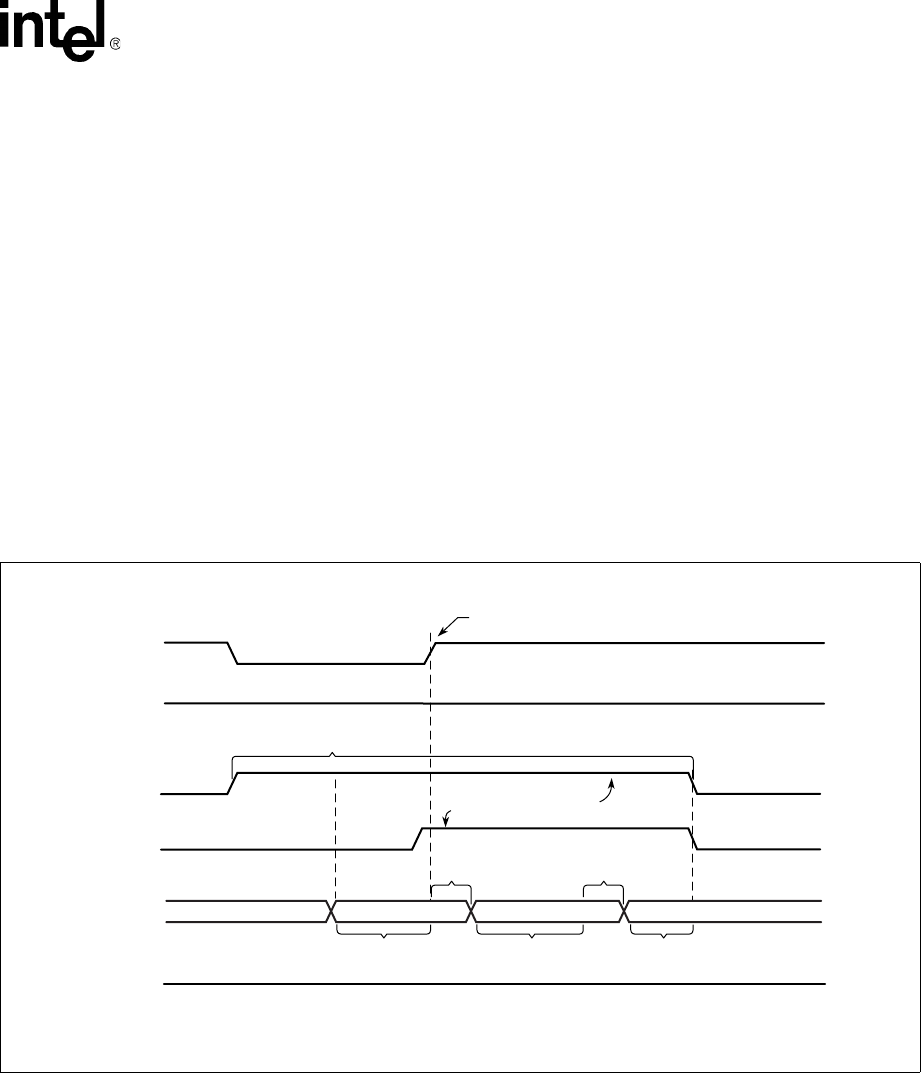

In the last scenario described above is shown in Figure 13-14.

As shown in the figure, reset does not invalidate the instruction cache because of the processor is in

Halt Mode. Since the instruction cache was not invalidated, it may contain valid lines. The host

must avoid downloading code to virtual addresses that are already valid in the instruction cache

(mini IC or main IC), otherwise the processor may behave unpredictably.

There are several possible solutions that ensure code is not downloaded to a VA that already exists

in the instruction cache.

1) Since the mini instruction cache was not invalidated, any code previously downloaded into

the mini IC is valid in the mini IC, so it is not necessary to download the same code again.

Figure 13-13. Code Download During a Warm Reset For Debug

B1311-01

RESET# pin assert until hold_rst signal is set

RESET does not affect Mini IC (Halt Mode Bit set)

hold_rst keeps internal

reset asserted

wait 2030 tcks after

RESET# asserted

Set hold_rst signal

Keep Halt Mode bit set

clock 15 tcks after

last update_dr in LDIC mode

SELDCSRSELDCSR LDICJTAG IR

Enter LDIC mode

Load code into IC

Clear hold_rst signal

Keep Halt Mode bit set

hold_rst

RESET#

Pin

TRST#

Halt Mode

JTAG IR

Internal

RESET