14-4 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Considerations

• Minimum Resource Latency

The minimum cycle distance from the issue clock of the current multiply instruction to the

issue clock of the next multiply instruction assuming the second multiply does not incur a data

dependency and is immediately available from the instruction cache or memory interface.

For the following code fragment, here is an example of computing latencies:

Table 14-3 shows how to calculate Issue Latency and Result Latency for each instruction. Looking

at the issue column, the UMLAL instruction starts to issue on cycle 0 and the next instruction,

ADD, issues on cycle 2, so the Issue Latency for UMLAL is two. From the code fragment, there is

a result dependency between the UMLAL instruction and the SUB instruction. In Table 14-3,

UMLAL starts to issue at cycle 0 and the SUB issues at cycle 5. thus the Result Latency is five.

14.4.2 Branch Instruction Timings

Example 14-1. Computing Latencies

UMLALr6,r8,r0,r1

ADD r9,r10,r11

SUB r2,r8,r9

MOV r0,r1

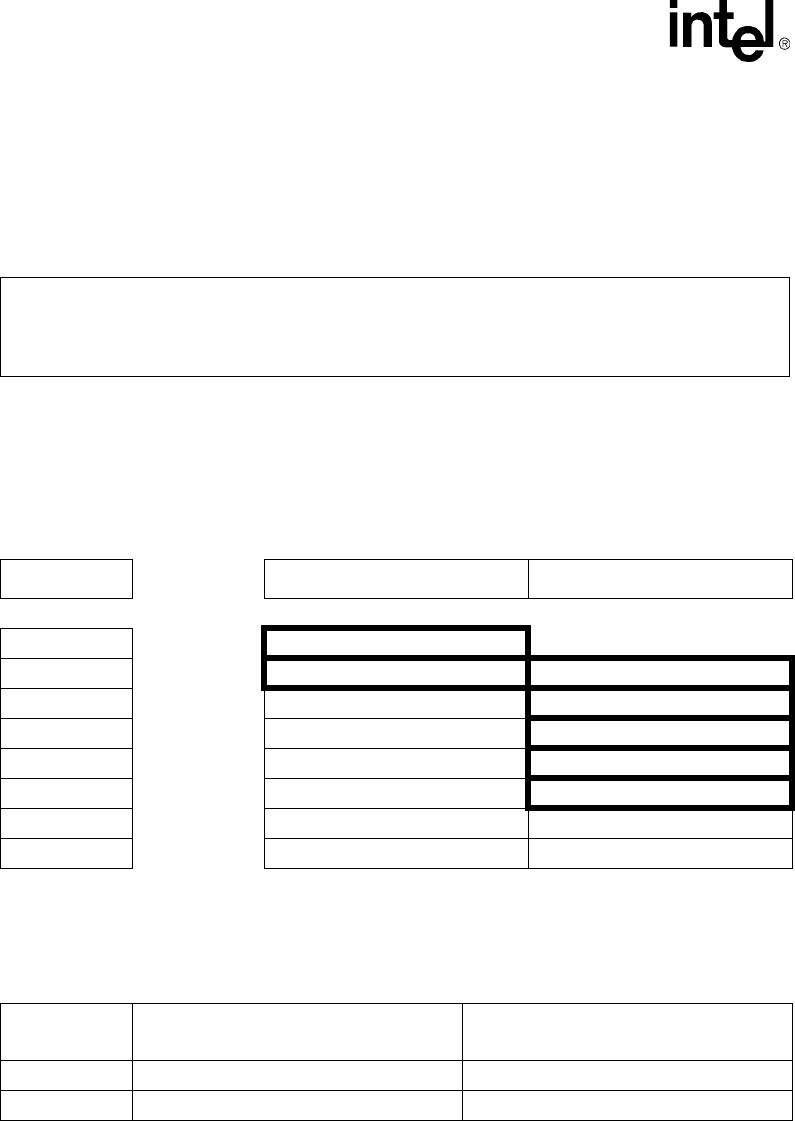

Table 14-3. Latency Example

Cycle Issue Executing

0 umlal (1st cycle) --

1 umlal (2nd cycle) umlal

2 add umlal

3 sub (stalled) umlal & add

4 sub (stalled) umlal

5 sub umlal

6 mov sub

7-- mov

Table 14-4. Branch Instruction Timings (Those predicted by the BTB)

Mnemonic

Minimum Issue Latency when Correctly

Predicted by the BTB

Minimum Issue Latency with Branch

Misprediction

B1 5

BL 1 5