9-4 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Interrupts

9.3.2 INTSRC

The Interrupt Source register (INTSRC) indicates which interrupts are active.

This register may be used by an ISR to determine quickly the source of an interrupt. Even if an

interrupt is masked with INTCTL, software may still detect whether it is asserted by reading its bit

from INTSRC.

Note that memory buffering and external logic on FIQ# and IRQ# could cause INTSRC.II and

INTSRC.FI to remain asserted for several cycles after the interrupt source has been commanded to

stop asserting. An ISR should ensure that the interrupt source is quelled, or a spurious recursive

entry to the ISR may result when interrupts are enabled.

Example 9-1 on page 9-4, shows how software might wait for the FIQ# signal to be deasserted

before proceeding.

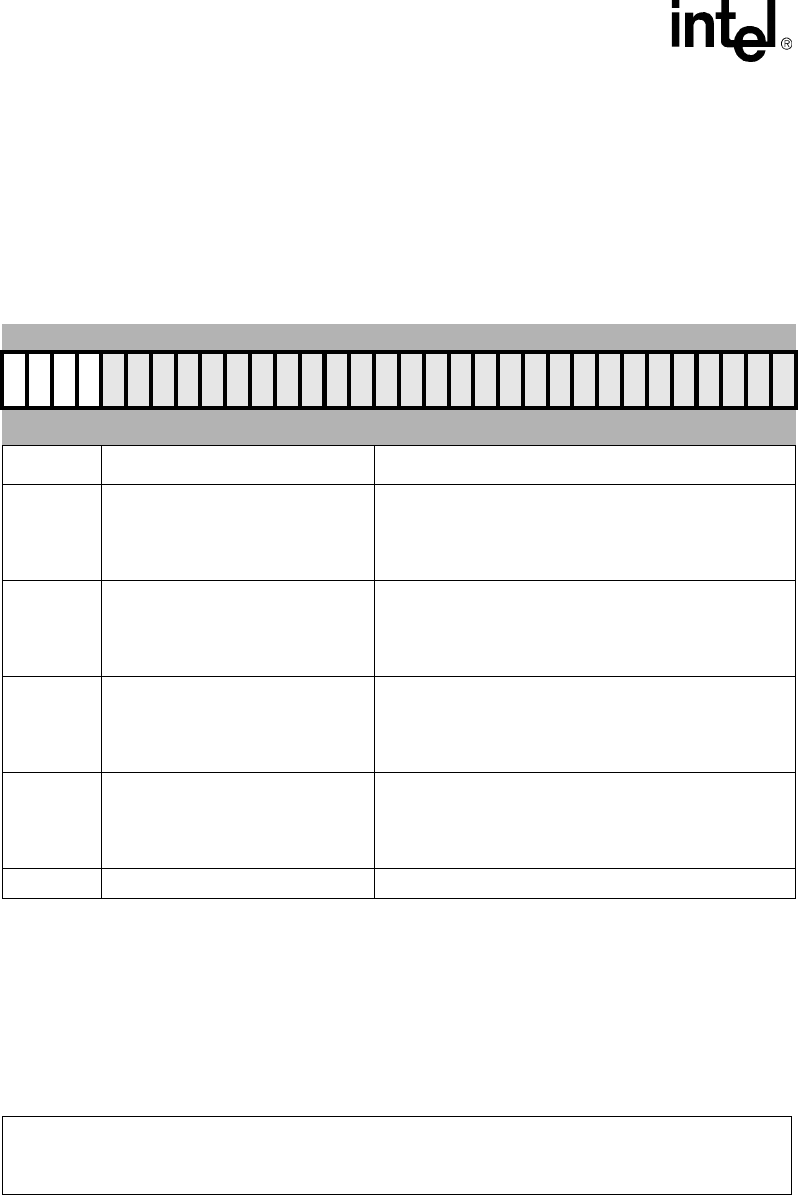

Table 9-2. Interrupt Source Register (CP13, register 4)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

F

I

I

I

B

I

P

I

reset value: undefined

Bits Access Description

31 Read / Write-ignored

FI - FIQ# active

Holds the state of the synchronized FIQ# signal.

0 = not interrupting

1 = interrupting

30 Read / Write-ignored

II - IRQ# active

Holds the state of the synchronized IRQ# signal.

0 = not interrupting

1 = interrupting

29 Read / Write-ignored

BI - BCU Interrupt Active

Holds the state of the BCU interrupt request.

0 = BCU not interrupting

1 = BCU interrupting

28 Read / Write-ignored

PI -PMU Interrupt Active

Holds the state of the PMU interrupt request.

0 = not interrupting

1 = interrupting

27:0 Read-unpredictable / Write-ignored Reserved

Example 9-1. Waiting for FIQ# Deassertion

waitForNoFIQ:

MRC P13, 0, R15, C4, C0, 0; get high bits of INTSRC into flags

BMI waitForNoFIQ; if FI bit set, try again