13-18 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.11.2 SELDCSR JTAG Register

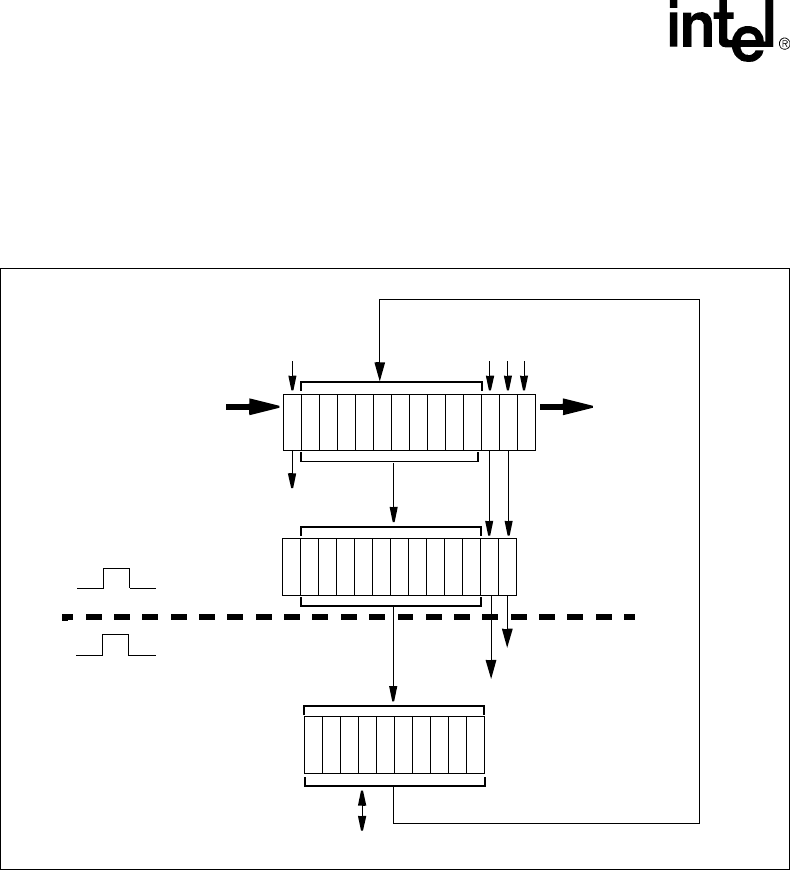

Placing the “SELDCSR” JTAG instruction in the JTAG IR, selects the DCSR JTAG Data register

(Figure 13-1), allowing the debugger to access the DCSR, generate an external debug break, set the

hold_rst signal, which is used when loading code into the instruction cache during reset.

A Capture_DR loads the current DCSR value into DBG_SR[34:3]. The other bits in DBG_SR are

loaded as shown in Figure 13-1.

A new DCSR value can be scanned into DBG_SR, and the previous value out, during the Shift_DR

state. When scanning in a new DCSR value into the DBG_SR, care must be taken to also set up

DBG_SR[2:1] to prevent undesirable behavior.

Update_DR parallel loads the new DCSR value into DBG_REG[33:2]. This value is then loaded

into the actual DCSR register. All bits defined as JTAG writable in Table 13-1, “Debug Control

and Status Register (DCSR)” on page 13-3 are updated.

An external host and the debug handler running on the Intel

®

80200 processor must synchronize

access the DCSR. If one side writes the DCSR at the same side the other side reads the DCSR, the

results are unpredictable.

Figure 13-1. SELDCSR Hardware

TDOTDI

DBG_SR

Capture_DR

Update_DR

DBG_REG

123

3435

031

software read/write

DCSR

TCK

Intel

®

80200 Processor

00

0

1 0

12

3334

0

ignored

hold_rst

external debug break

CLK