10-22 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

10.3.8 Locked Access

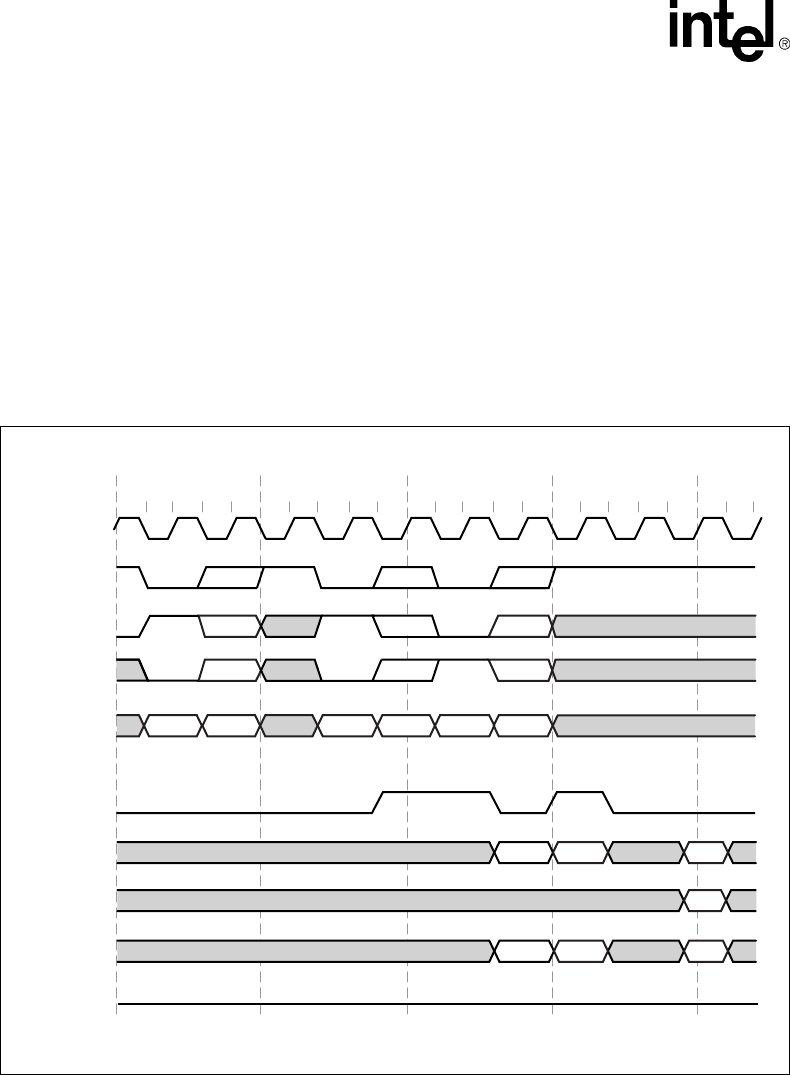

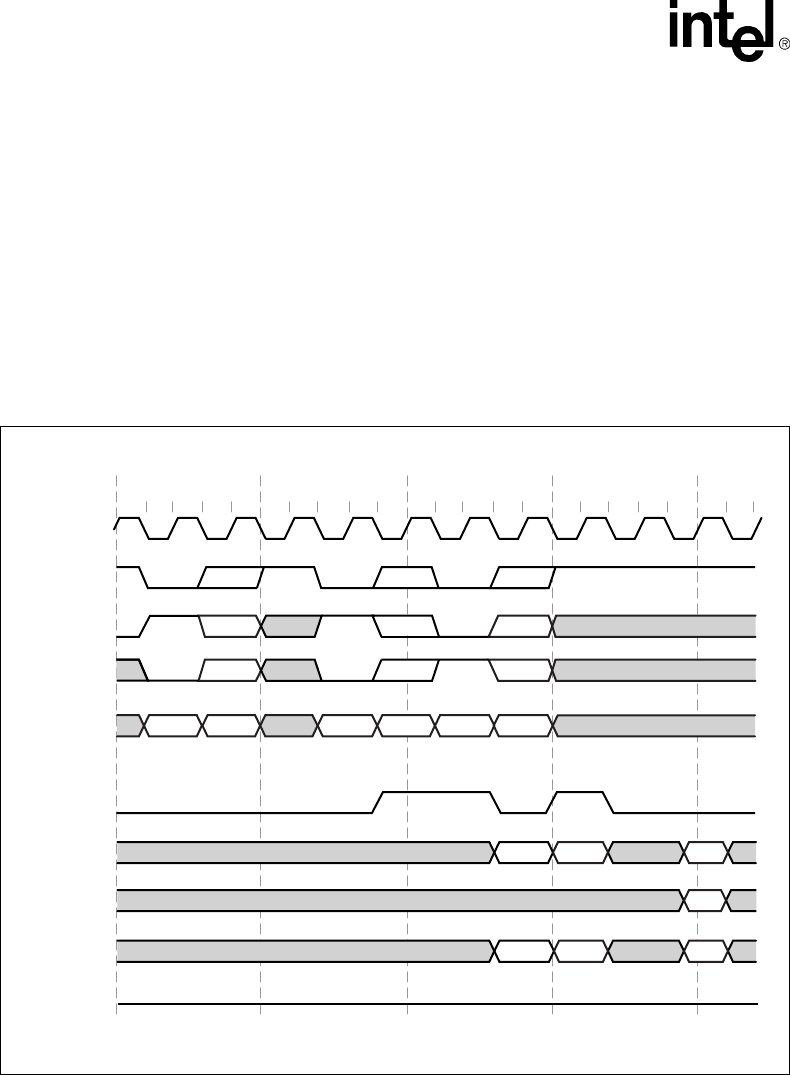

An example of a locked access is shown in Figure 10-12. Here the processor is doing an atomic

read/write to address 0x240, denoted as A in the figure. The Lock signal, which is valid at the

positive edge of MCLK when ADS# is asserted, are asserted for each request from the read of A

just prior to the matching write of A.

Note that an intervening read cycle to location 0x12349988 also occurs, perhaps to read a page

table element. This is legal behavior and must be accommodated by all entities on the bus. The bus

makes no guarantee as to how many cycles may elapse between a locked read and its

corresponding locked write. It is guaranteed that no writes intervene during that period, although

an arbitrary number of reads may occur.

Figure 10-12. Locked Access

B1308-01

0x0 0x240 0x0 0x240

0ns 50ns 75ns 100ns25ns

MCLK

ADS#/LEN

(2)

Lock/LEN

(1)

W/R#/LEN

(0)

A

DValid

D

BE#

DCB

Rd A Rd B Wr A

Abort

Rd A

0

Rd B Wr A

0

1

1

0x1243

0

1

00

0

0xF0

0x9988