Developer’s Manual March, 2003 14-9

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Considerations

14.4.8 Semaphore Instructions

14.4.9 Coprocessor Instructions

14.4.10 Miscellaneous Instruction Timing

14.4.11 Thumb* Instructions

The timing of Thumb instructions are the same as their equivalent ARM instructions. This mapping

can be found in the ARM Architecture Reference Manual. The only exception is the Thumb BL

instruction when H = 0; the timing in this case would be the same as an ARM data processing

instruction.

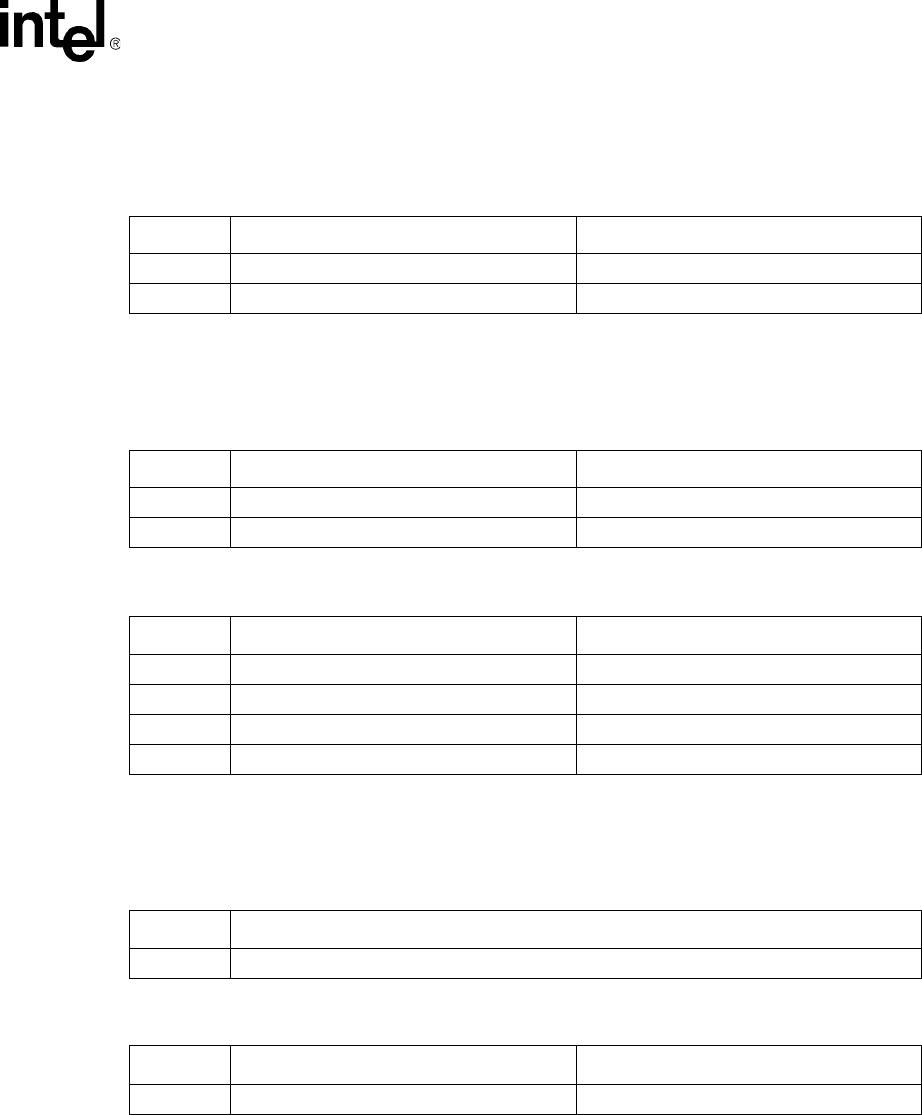

Table 14-14. Semaphore Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

SWP 5 5

SWPB 5 5

Table 14-15. CP15 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC 4 4

MCR 2 N/A

Table 14-16. CP14 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC 7 7

MCR 7 N/A

LDC 10 N/A

STC 7 N/A

Table 14-17. SWI Instruction Timings

Mnemonic Minimum latency to first instruction of SWI exception handler

SWI 6

Table 14-18. Count Leading Zeros Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

CLZ 1 1