12-6 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Monitoring

12.5 Performance Monitoring Events

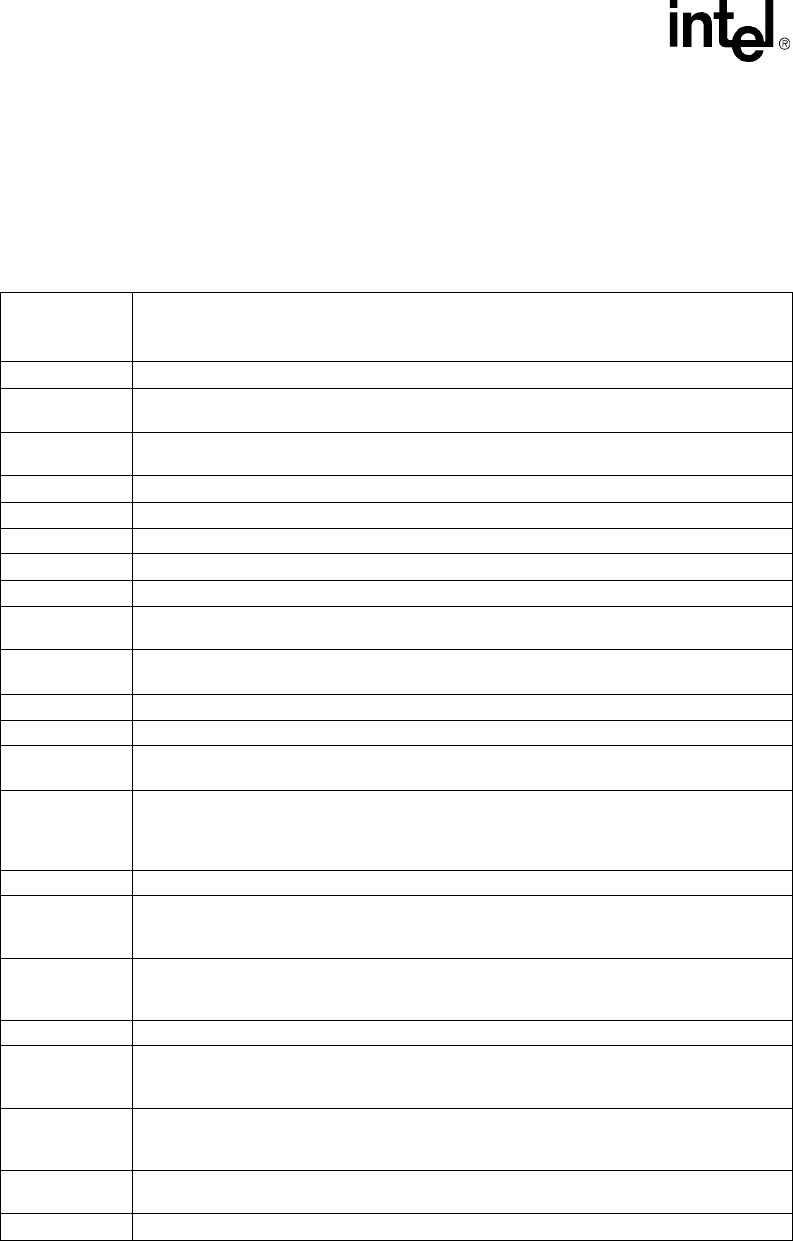

Table 12-4 lists events that may be monitored by the PMU. Each of the Performance Monitor

Count Registers (PMN0 and PMN1) can count any listed event. Software selects which event is

counted by each PMNx register by programming the evtCountx fields of the PMNC register.

Table 12-4. Performance Monitoring Events

Event Number

(evtCount0 or

evtCount1)

Event Definition

0x0 Instruction cache miss requires fetch from external memory.

0x1

Instruction cache cannot deliver an instruction. This could indicate an ICache miss or an

ITLB miss. This event occurs every cycle in which the condition is present.

0x2

Stall due to a data dependency. This event occurs every cycle in which the condition is

present.

0x3 Instruction TLB miss.

0x4 Data TLB miss.

0x5 Branch instruction executed, branch may or may not have changed program flow.

0x6 Branch mispredicted. (B and BL instructions only.)

0x7 Instruction executed.

0x8

Stall because the data cache buffers are full. This event occurs every cycle in which the

condition is present.

0x9

Stall because the data cache buffers are full. This event occurs once for each contiguous

sequence of this type of stall.

0xA Data cache access, not including Cache Operations (defined in Section 7.2.8)

0xB Data cache miss, not including Cache Operations (defined in Section 7.2.8)

0xC

Data cache write-back. This event occurs once for each 1/2 line (four words) that are

written back from the cache.

0xD

Software changed the PC. This event occurs any time the PC is changed by software and

there is not a mode change. For example, a mov instruction with PC as the destination

triggers this event. Executing a swi from User mode does not trigger this event, because it

incurs a mode change.

0x10 The BCU received a new memory request from the core.

0x11

The BCUs request queue is full. This event takes place each clock cycle in which the

condition is met. A high incidence of this event indicates the BCU is often waiting for

transactions to complete on the external bus.

0x12

The number of times the BCU queues were drained due to a Drain Write Buffer command

or an I/O transaction as identified by C = 0 and B = 0 (cacheable and bufferable page

attribute bits).

0x13 Reserved, unpredictable results.

0x14

The BCU detected an ECC error, but no ELOG register was available in which to log the

error. (See Section 11.4.2, “ECC Error Registers” on page 11-9 for a description of the

ELOG registers).

0x15

BCU detected a 1-bit error while reading data from the bus. This event may be counted

even if reporting of 1-bit errors is disabled. See Section 11.3, “Error Handling” on page 11-2

for a description of 1-bit errors.

0x16

RMW cycle occurred due to narrow write on ECC-protected memory (see Section 11.2,

“ECC” on page 11-1 for a description of ECC and RMW cycles).

all others Reserved, unpredictable results