Developer’s Manual March, 2003 13-31

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.13.1.3 Address Bytes

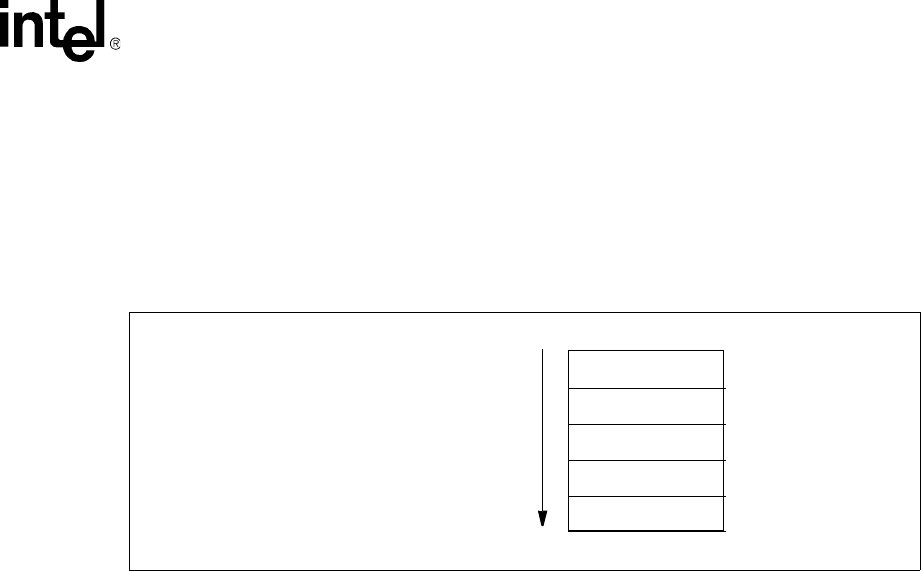

Only indirect branch entries contain address bytes in addition to the message byte. Indirect branch

entries always have four address bytes indicating the target of that indirect branch. When reading

the trace buffer the MSB of the target address is read out first; the LSB is the fourth byte read out;

and the indirect branch message byte is the fifth byte read out. The byte organization of the indirect

branch message is shown in Figure 13-8.

Figure 13-8. Indirect Branch Entry Address Byte Organization

target[31:24]

target[23:16]

target[15:8]

target[7:0]

indirect br msg

Trace buffer is read by

software in this

direction. The message

byte is always the last of

the 5 bytes in the entry

to be read.