7-2 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

The format of MRC and MCR is shown in Table 7-1.

cp_num is defined for CP15, CP14, CP13 and CP0. CP13 contains the interrupt controller and bus

controller registers and is described in Chapter 9, “Interrupts”and Chapter 11, “Bus Controller,”

respectively. CP0 supports instructions specific for DSP and is described in Chapter 2,

“Programming Model.” Access to all other coprocessors on the Intel

®

80200 processor causes an

undefined exception.

Unless otherwise noted, unused bits in coprocessor registers have unpredictable values when read.

For compatibility with future implementations, software should not rely on the values in those bits.

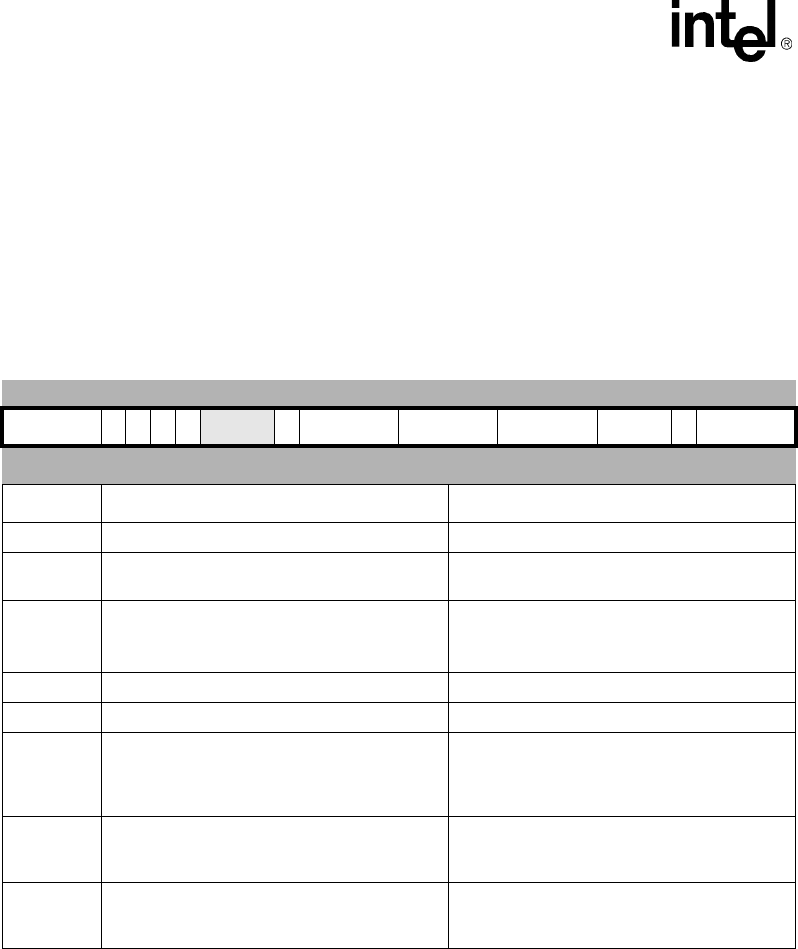

Table 7-1. MRC/MCR Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1110

opcode_1

n CRn Rd cp_num

opcode_2

1 CRm

Bits Description Notes

31:28 cond - ARM* condition codes -

23:21 opcode_1 - Reserved

Should be programmed to zero for future

compatibility

20

n - Read or write coprocessor register

0 = MCR

1 = MRC

-

19:16 CRn - specifies which coprocessor register -

15:12 Rd - General Purpose Register, R0..R15 -

11:8 cp_num - coprocessor number

0b1111 = CP15

0b1110 = CP14

0x1101 = CP13

0x0000 = CP0

7:5 opcode_2 - Function bits

This field should be programmed to zero for

future compatibility unless a value has been

specified in the command.

3:0 CRm - Function bits

This field should be programmed to zero for

future compatibility unless a value has been

specified in the command.