Developer’s Manual March, 2003 10-15

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

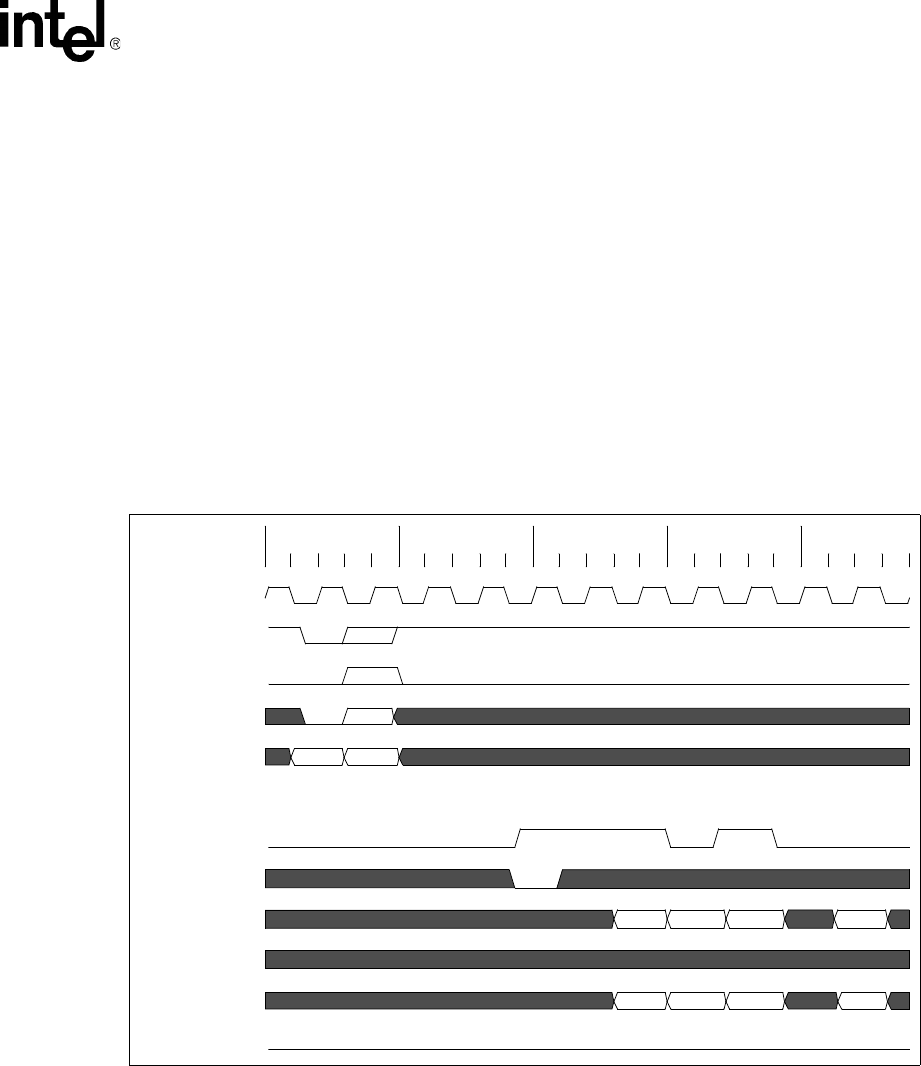

10.3.2 Read Burst, No Critical Word First

In Figure 10-5 the request goes out the same as the last example, with the address 0x248 this time

and the length 0x6, indicating an eight word cache line fill. The first data cycle begins at 50 ns with

DValid being asserted with CWF low to indicate that this burst starts at the lowest word pair and

return sequentially. Notice that the data returning is the eight word block beginning at 0x240, not

0x249. The low five bits of the address are not used for determining what data to return in a 32-byte

read request (cache line fill). DValid stays high for three cycles, drops for a cycle, and then is

asserted for one more cycle.

Two clocks after each clock where DValid is sampled high, the next sequential pair of data words

is driven on the bus. This data can come back to back in sequential cycles (as it likely would from a

burst SDRAM, for example), or can be spaced further apart, as shown by the last data cycle here.

Each data cycle in the transaction is independent of the others in timing, as long as the order of

cycles in the transaction is maintained consistent with the CWF value asserted on the first data

cycle.

Figure 10-5. Read Burst, No CWF

Rd Req

0x0

No Wrap

0x240 0x248 0x250 (0x258

ECC

0x248

1

1

0

0ns 25ns 50ns 75ns 100ns

MCLK

ADS#/LEN[2]

Lock/LEN[1]

W/R#/LEN[0]

A

DValid

CWF

D

BE#

DCB

Abort