Developer’s Manual March, 2003 2-7

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

2.3.1.2 Internal Accumulator Access Format

The Intel

®

80200 processor defines a new instruction format for accessing internal accumulators in

CP0. Table 2-5, “Internal Accumulator Access Format” on page 2-7 shows that the opcode falls

into the coprocessor register transfer space.

The RdHi and RdLo fields allow up to 64 bits of data transfer between Intel

®

StrongARM*

registers and an internal accumulator. The acc field specifies 1 of 8 internal accumulators to

transfer data to/from. The Intel

®

80200 processor implements a single 40-bit accumulator referred

to as acc0; future implementations can specify multiple internal accumulators of varying sizes, up

to 64 bits.

Access to the internal accumulator is allowed in all processor modes (user and privileged) as long

bit 0 of the Coprocessor Access Register is set. (See Section 7.2.15, “Register 15: Coprocessor

Access Register” on page 7-18 for more details).

The Intel

®

80200 processor implements two instructions MAR and MRA that move two Intel

®

StrongARM* registers to acc0 and move acc0 to two Intel

®

StrongARM* registers, respectively.

Note: MAR has the same encoding as MCRR (to coprocessor 0) and MRA has the same encoding as

MRRC (to coprocessor 0). These instructions move 64-bits of data to/from ARM registers from/to

coprocessor registers. MCRR and MRRC are defined in ARM’s DSP instruction set.

Disassemblers not aware of MAR and MRA produces the following syntax:

MCRR{<cond>} p0, 0x0, RdLo, RdHi, c0

MRRC{<cond>} p0, 0x0, RdLo, RdHi, c0

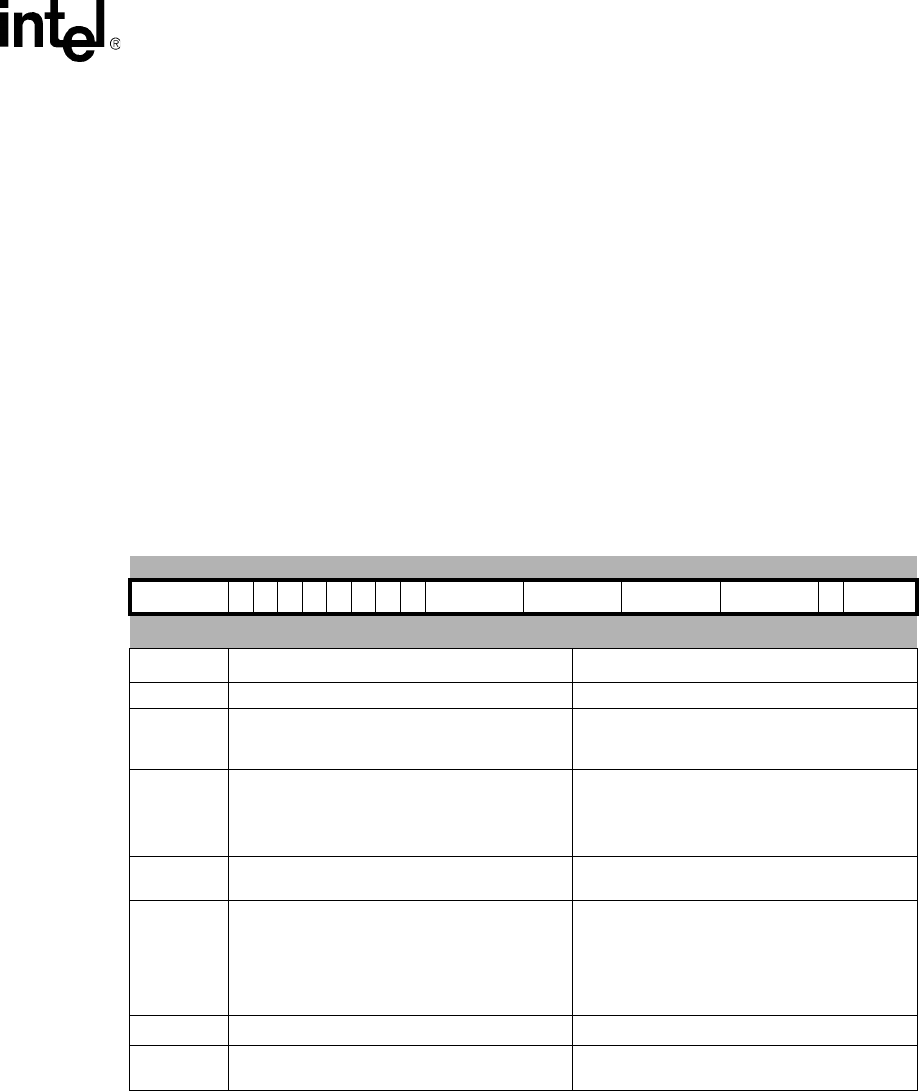

Table 2-5. Internal Accumulator Access Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1100010L RdHi RdLo 000000000 acc

Bits Description Notes

31:28 cond - ARM condition codes -

20

L - move to/from internal accumulator

0= move to internal accumulator (MAR)

1= move from internal accumulator (MRA)

-

19:16

RdHi - specifies the high order eight (39:32)

bits of the internal accumulator.

On a read of the acc, this 8-bit high order field

is sign extended.

On a write to the acc, the lower 8 bits of this

register is written to acc[39:32]

15:12

RdLo - specifies the low order 32 bits of the

internal accumulator

-

7:4 Should be zero

This field could be used in future

implementations to specify the type of

saturation to perform on the read of an internal

accumulator. (e.g., a signed saturation to

16-bits may be useful for some filter

algorithms.)

3 Should be zero

-

2:0 acc - specifies 1 of 8 internal accumulators

Intel

®

80200 processor only implements acc0;

access to any other acc is unpredictable