13-6 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.5 Debug Exceptions

A debug exception causes the processor to re-direct execution to a debug event handling routine.

The Intel

®

80200 processor debug architecture defines the following debug exceptions:

• instruction breakpoint

• data breakpoint

• software breakpoint

• external debug break

• exception vector trap

• trace-buffer full break

When a debug exception occurs, the processor’s actions depend on whether the debug unit is

configured for Halt mode or Monitor mode.

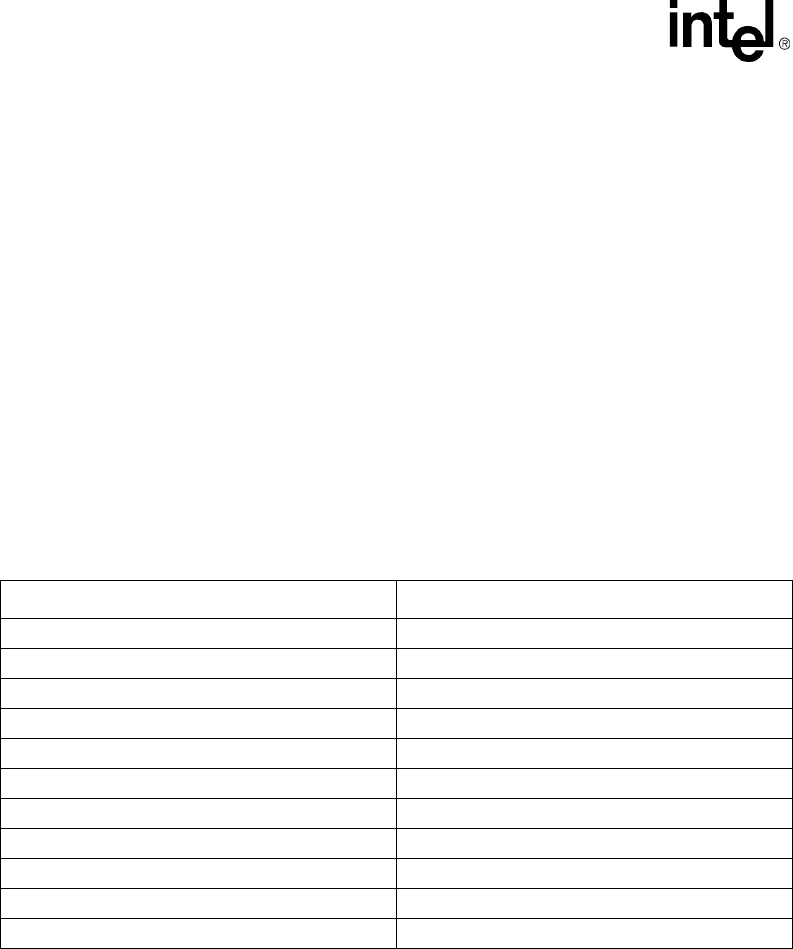

Table 13-2 shows the priority of debug exceptions relative to other processor exceptions.

13.5.1 Halt Mode

The debugger turns on Halt mode through the JTAG interface by scanning in a value that sets the

bit in DCSR. The debugger turns off Halt mode through JTAG, either by scanning in a new DCSR

value or by a TRST. Processor reset does not effect the value of the Halt mode bit.

When halt mode is active, the processor uses the reset vector as the debug vector. The debug

handler and exception vectors can be downloaded directly into the instruction cache, to intercept

the default vectors and reset handler, or they can be resident in external memory. Downloading into

the instruction cache allows a system with memory problems, or no external memory, to be

debugged. Refer top Section 13.14, “Downloading Code in the ICache” on page 13-34 for details

about downloading code into the instruction cache.

Table 13-2. Event Priority

Event Priority

Reset 1

Vector Trap 2

data abort (precise) 3

data bkpt 4

data abort (imprecise) 5

external debug break, trace-buffer full 6

FIQ 7

IRQ 8

instruction breakpoint 9

pre-fetch abort 10

undef, SWI, software Bkpt 11