Developer’s Manual March, 2003 14-5

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Considerations

14.4.3 Data Processing Instruction Timings

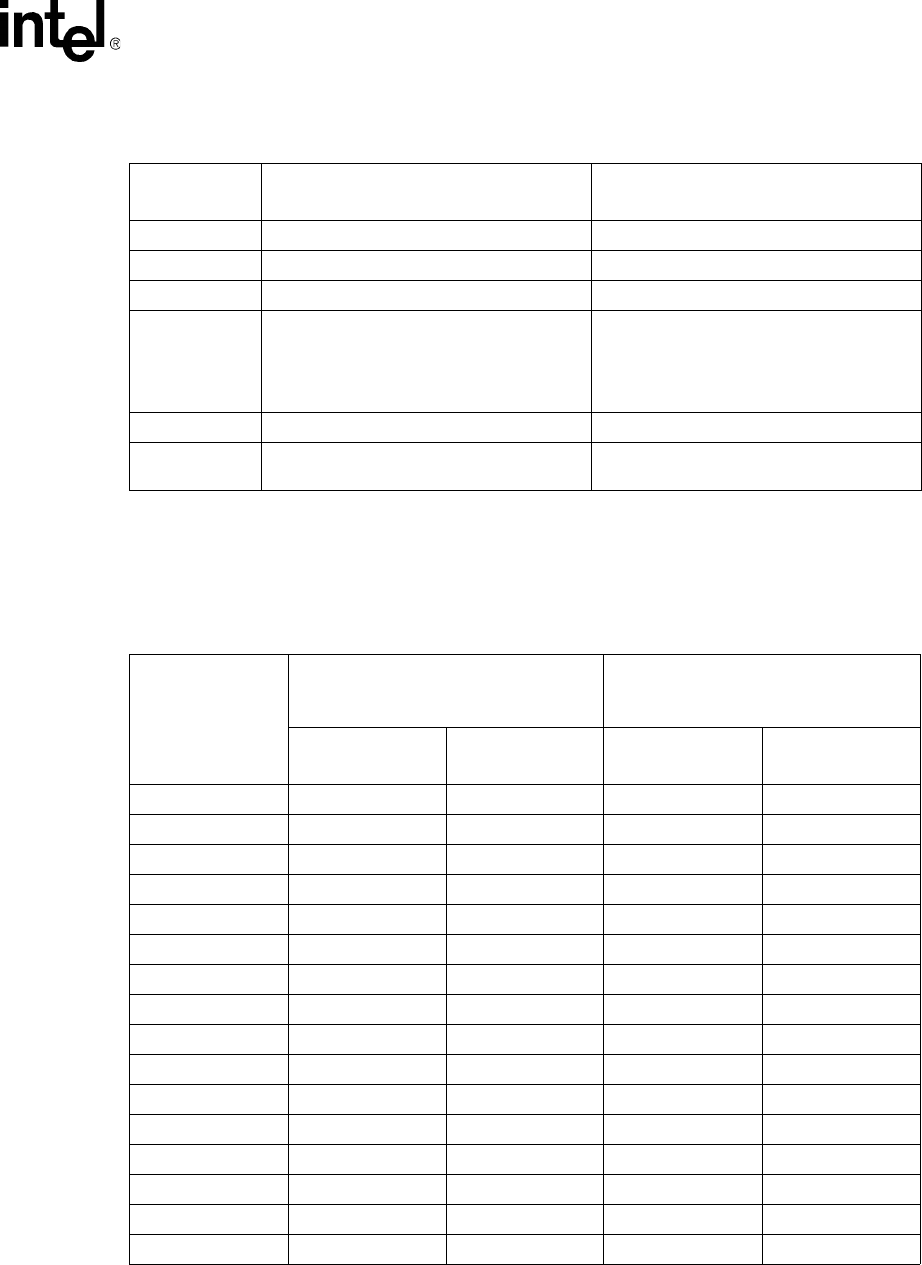

Table 14-5. Branch Instruction Timings (Those not predicted by the BTB)

Mnemonic

Minimum Issue Latency when Branch

Not Taken

Minimum Issue Latency when Branch

Taken

BLX(1) N/A 5

BLX(2) 1 5

BX 1 5

Data

Processing

Instruction with

PC as the

destination

Same as Table 14-6 4 + numbers in Table 14-6

LDR PC, <> 2 8

LDM with PC in

register list

3 + numreg

1

1. numreg is the number of registers in the register list including the PC.

10 + max (0, numreg-3)

Table 14-6. Data Processing Instruction Timings

Mnemonic

<shifter operand> is NOT a Shift/Rotate

by Register

<shifter operand> is a Shift/Rotate by

Register OR

<shifter operand> is RRX

Minimum Issue

Latency

Minimum Result

Latency

1

1. If the next instruction needs to use the result of the data processing for a shift by immediate or as Rn in a QDADD or QDSUB,

one extra cycle of result latency is added to the number listed.

Minimum Issue

Latency

Minimum Result

Latency

1

ADC1122

ADD1122

AND1122

BIC1122

CMN1122

CMP1122

EOR1122

MOV1122

MVN1122

ORR1122

RSB1122

RSC1122

SBC1122

SUB1122

TEQ1122

TST1122