Developer’s Manual March, 2003 10-23

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

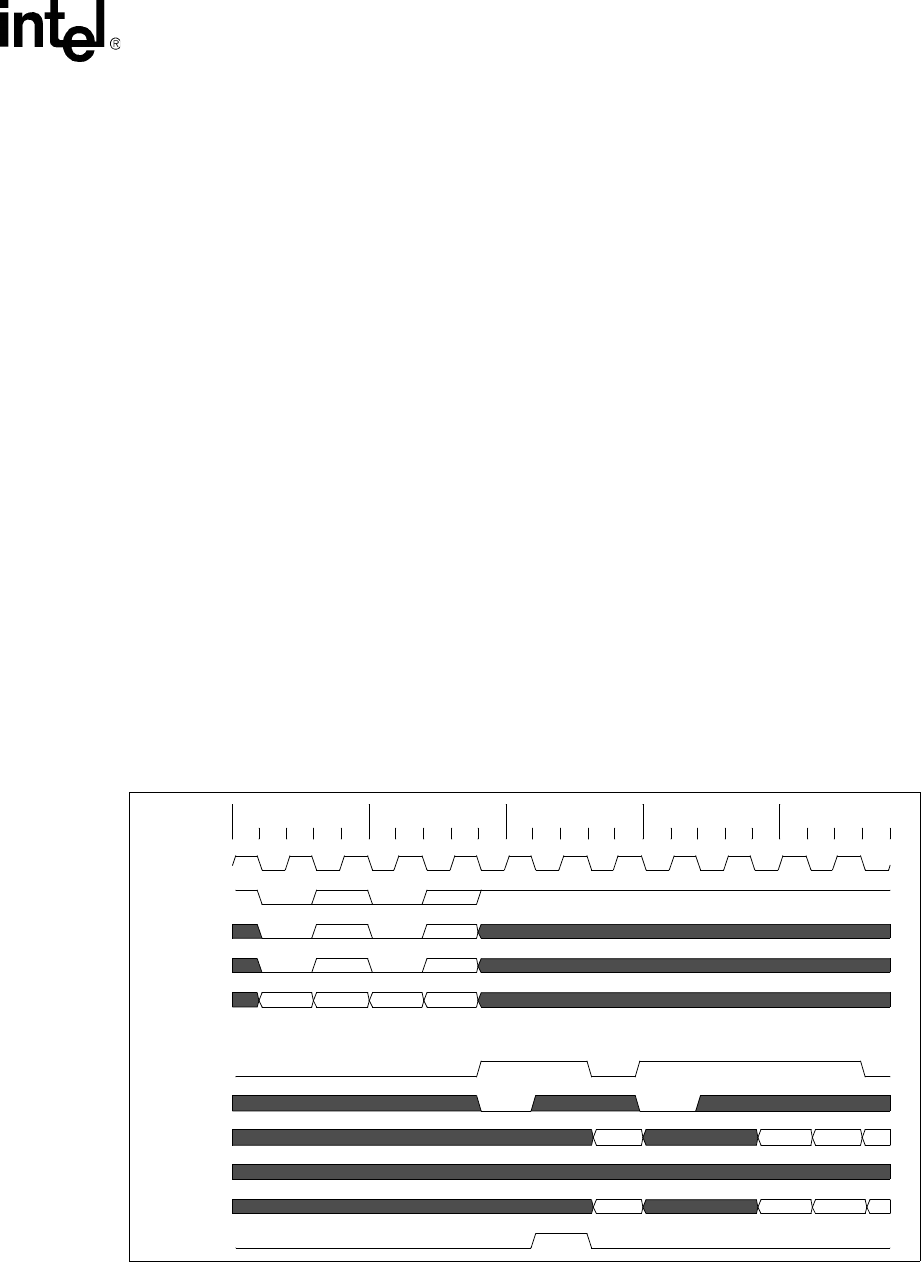

10.3.9 Aborted Access

As discussed in Section 10.2.6, “Abort” on page 10-11, any request from the Intel

®

80200

processor can be aborted by the chipset or memory. This might occur if there was a PCI error, or if

a request was issued to unimplemented memory. Figure 10-13 shows an aborted read. Read A is

issued at time 10 ns for 32 bytes of data. At 50 ns DValid goes high to indicate the beginning of the

first data cycle. Abort is not asserted along with this DValid assertion. At 60 ns, DValid for the

second data cycle is asserted, and this time Abort is asserted. This indicates that this transaction is

aborted and no more data cycles begin for this transaction. Notice, however, that the first data cycle

begun with the DValid assertion at 50 ns is still ongoing, and the Intel

®

80200 processor latches

that data and return it to the core as valid data.

If transaction A was a write request rather than a read, the Intel

®

80200 processor would drive data

onto the bus at time 70 ns, as requested by the DValid with Abort NOT asserted at 50 ns. No data

would be driven at time 80 ns because the DValid at time 60 ns had Abort asserted high.

When the Abort data cycle occurs, the Intel

®

80200 processor ends that transaction and expect no

further data on it. When DValid next goes high at time 80 ns, the Intel

®

80200 processor expects a

data cycle associated with the next transaction, in this case the first data cycle of read B.

If an aborted data burst cannot be stopped by the memory system, it is sufficient to allow it to

complete with DValid deasserted. This is a slight bandwidth hit, but aborts should be rare.

If, during a locked access, any read access encounters an Abort, the Intel

®

80200 processor still

emits the final unlocking write. If the final unlocking write is an Abort, the bus is still unlocked

with the write. The Intel

®

80200 processor never fails to deassert Lock.

External logic must leave a gap of at least one MCLK cycle between aborts to the Intel

®

80200

processor.

Figure 10-13. Aborted Access

Rd A Rd B.

0x0 0x0

Data A0 Data B0Data B1Data B2

Abort A.

0x240

1

1

0

0x260

0

1

1

0ns 25ns 50ns 75ns 100ns

MCLK

ADS#/LEN[2]

Lock/LEN[1]

W/R#/LEN[0]

A

DValid

CWF

D

BE#

DCB

Abort