13-10 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.6.2 Data Breakpoints

The Intel

®

80200 processor debug architecture defines two data breakpoint registers (DBR0,

DBR1). The format of the registers is shown in Table 13-4.

DBR0 is a dedicated data address breakpoint register. DBR1 can be programmed for 1 of 2

operations:

• data address mask

• second data address breakpoint

The DBCON register controls the functionality of DBR1, as well as the enables for both DBRs.

DBCON also controls what type of memory access to break on.

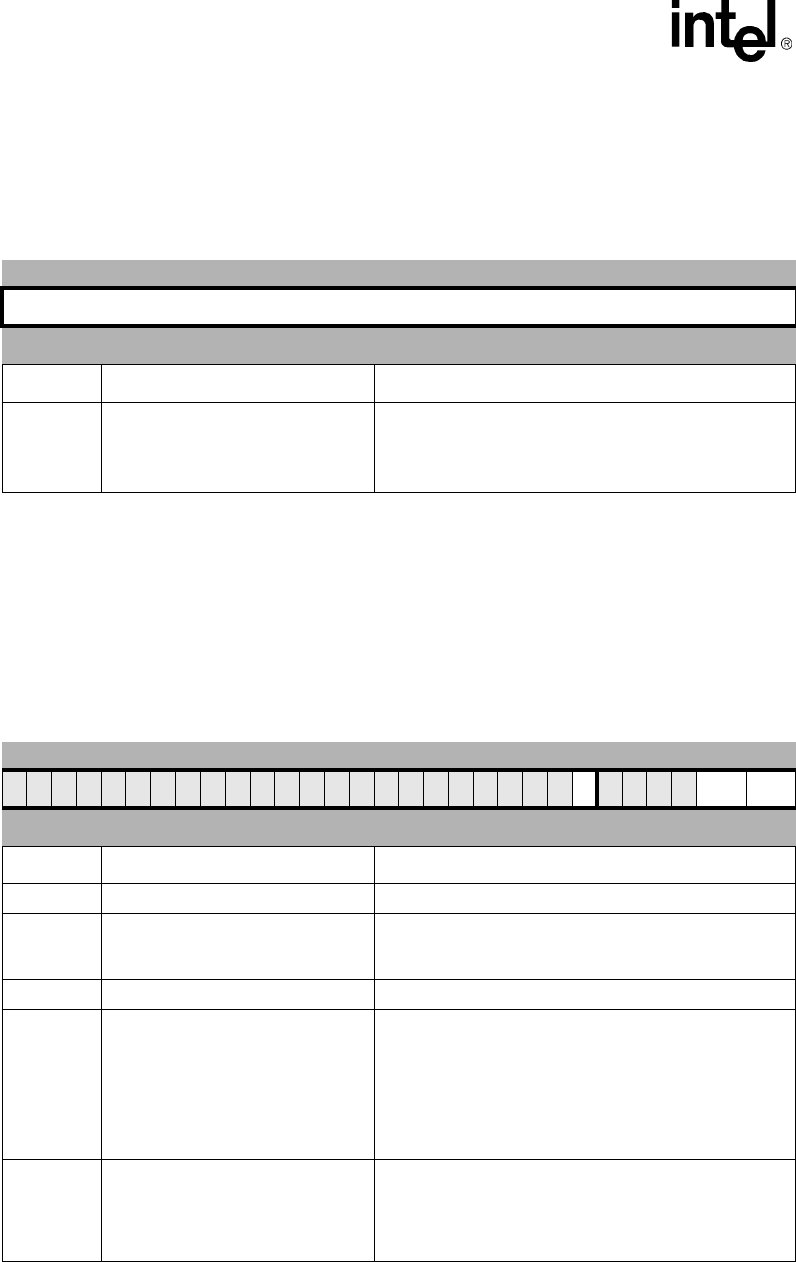

Table 13-4. Data Breakpoint Register (DBRx)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DBRx

reset value: unpredictable

Bits Access Description

31:0 Read / Write

DBR0: Data Breakpoint MVA

DBR1:

Data Address Mask OR

Data Breakpoint MVA

Table 13-5. Data Breakpoint Controls Register (DBCON)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

M E1 E0

reset value: 0x00000000

Bits Access Description

31:9 Read-as-Zero / Write-ignored Reserved

8 Read / Write

DBR1 Mode (M) -

0: DBR1 = Data Address Breakpoint

1: DBR1 = Data Address Mask

7:4 Read-as-Zero / Write-ignored Reserved

3:2 Read / Write

DBR1 Enable (E1) -

When DBR1 = Data Address Breakpoint

0b00: DBR1 disabled

0b01: DBR1 enabled, Store only

0b10: DBR1 enabled, Any data access, load or store

0b11: DBR1 enabled, Load only

When DBR1 = Data Address Mask this field has no effect

1:0 Read / Write

DBR0 Enable (E0) -

0b00: DBR0 disabled

0b01: DBR0 enabled, Store only

0b10: DBR0 enabled, Any data access, load or store

0b11: DBR0 enabled, Load only