Developer’s Manual March, 2003 11-3

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Bus Controller

11.3.2 ECC Errors

An ECC error occurs when the BCU reads data and notices that the associated ECC bits do not

match the data. This could also happen as a result of the RMW that the BCU performs on sub

bus-width writes. A single transaction on the bus could result in multiple ECC errors, as the BCU

checks each bus-width entity as it is received. Table 11-1 summarizes the BCU error response for

ECC errors. The response is tailorable; some of the actions may be disabled, such as requesting a

core interrupt. See Section 11.4.1, “BCU Control Registers” on page 11-5, for information on the

EE, and SR bits, and how the BCU error response may be altered.

In all cases, the BCU attempts the additional response of logging the error into a register. If register

ELOG0 is not already being used to record an error, the BCU logs error information into registers

ELOG0 and ECAR0. If ELOG0 already has error information, but ELOG1 does not, the BCU uses

ELOG1 and ECAR1 to log the error. If both ELOG0 and ELOG1 are in use, the BCU sets the error

overflow bit (register BCUCTL, bit EV). A description of these registers is in Section 11.4.1 and

Section 11.4.2.

When an error is detected during a RMW, the BCU writes the corrupted data back to memory

because it needs to finish the atomic transaction. If it did not do this, an external bus agent might

consider the bus to be permanently locked. The BCU does not assert any of the byte enables (nBE)

when writing the corrupted data back. A memory system should use this as an indication to not

update the DCB value or any data bytes.

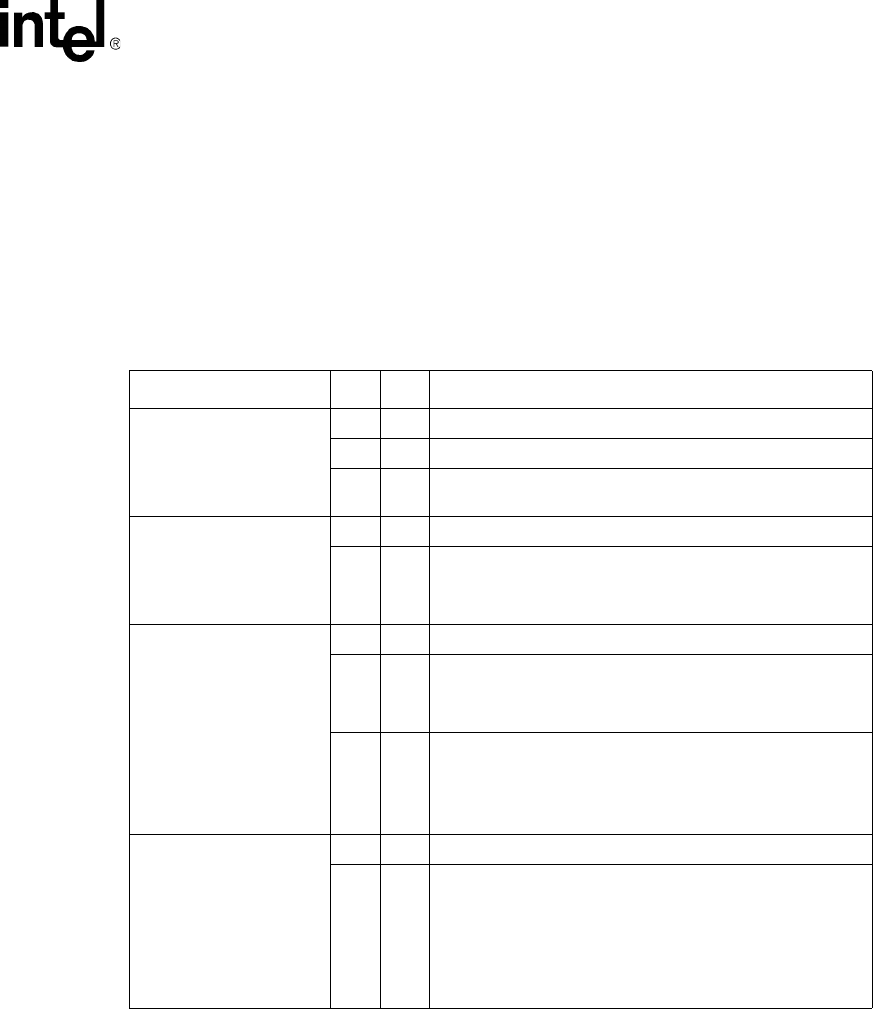

Table 11-1. BCU Response to ECC Errors

Event EE SR Response

Read with 1-bit error

0 - No correction, no notification

10• Correction if BCUCTL.SC = 1

11

• Correction if BCUCTL.SC = 1

Request core interrupt

Read with multi-bit error

0 - No notification

1-

• If transaction is a data read: imprecise data abort

• If transaction is an instruction fetch: prefetch abort

• If transaction is an MMU operation: precise data abort

RMW with 1-bit error from

the read cycle

0 - Does not occur -- RMW only if BCUCTL.EE = 1

10

• Correction if BCUCTL.SC = 1

• Merge store data with data from read

• Write updated data to memory

11

• Correction if BCUCTL.SC = 1

• Merge store data with data from read

• Write updated data to memory

• Request core interrupt

RMW with multi-bit error

from the read cycle

0 - Does not occur -- RMW only if BCUCTL.EE = 1

1-

• Merge store data with data from read

• Write updated data to memory with deasserted byte

enables

• If transaction is a data read: imprecise data abort

• If transaction is an instruction fetch: prefetch abort

• If transaction is an MMU operation: precise data abort