Developer’s Manual March, 2003 3-3

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Memory Management

3.2.2.4 Data Cache and Write Buffer

All of these descriptor bits affect the behavior of the Data Cache and the Write Buffer.

If the X bit for a descriptor is zero, the C and B bits operate as mandated by the ARM architecture.

This behavior is detailed in Table 3-1.

If the X bit for a descriptor is one, the C and B bits’ meaning is extended, as detailed in Table 3-2.

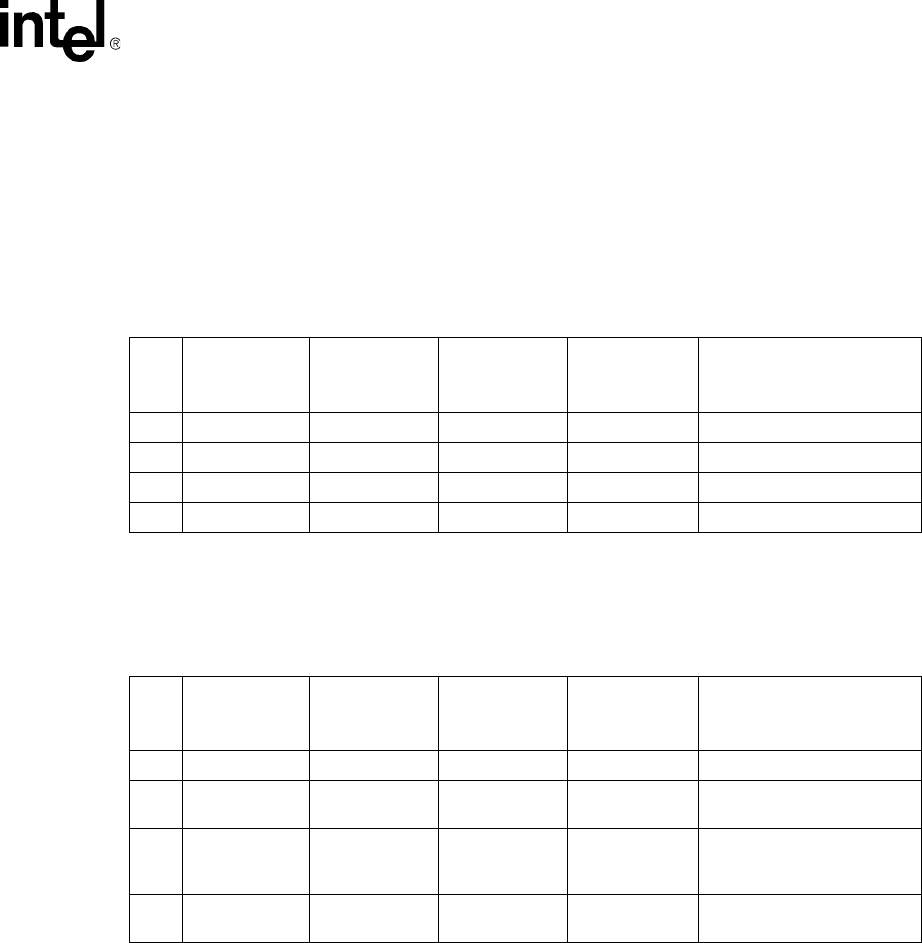

Table 3-1. Data Cache and Buffer Behavior when X = 0

C B Cacheable? Bufferable? Write Policy

Line

Allocation

Policy

Notes

0 0 N N - - Stall until complete

a

a. Normally, the processor continues executing after a data access if no dependency on that access is encountered. With this

setting, the processor stalls execution until the data access completes. This guarantees to software that the data access has

taken effect by the time execution of the data access instruction completes. External data aborts from such accesses are

imprecise (but see Section 2.3.4.4 for a method to shield code from this imprecision).

0 1 N Y - -

1 0 Y Y Write Through Read Allocate

1 1 Y Y Write Back Read Allocate

Table 3-2. Data Cache and Buffer Behavior when X = 1

C B Cacheable? Bufferable? Write Policy

Line

Allocation

Policy

Notes

0 0 - - - - Unpredictable -- do not use

0 1 N Y - -

Writes do not coalesce into

buffers

a

a. Normally, bufferable writes can coalesce with previously buffered data in the same address range

1 0

(Mini Data

Cache)

---

Cache policy is determined

by MD field of Auxiliary

Control register

b

b. See Section 7.2.2 for a description of this register

1 1 Y Y Write Back

Read/Write

Allocate