1-2 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Introduction

1.1.2 Features

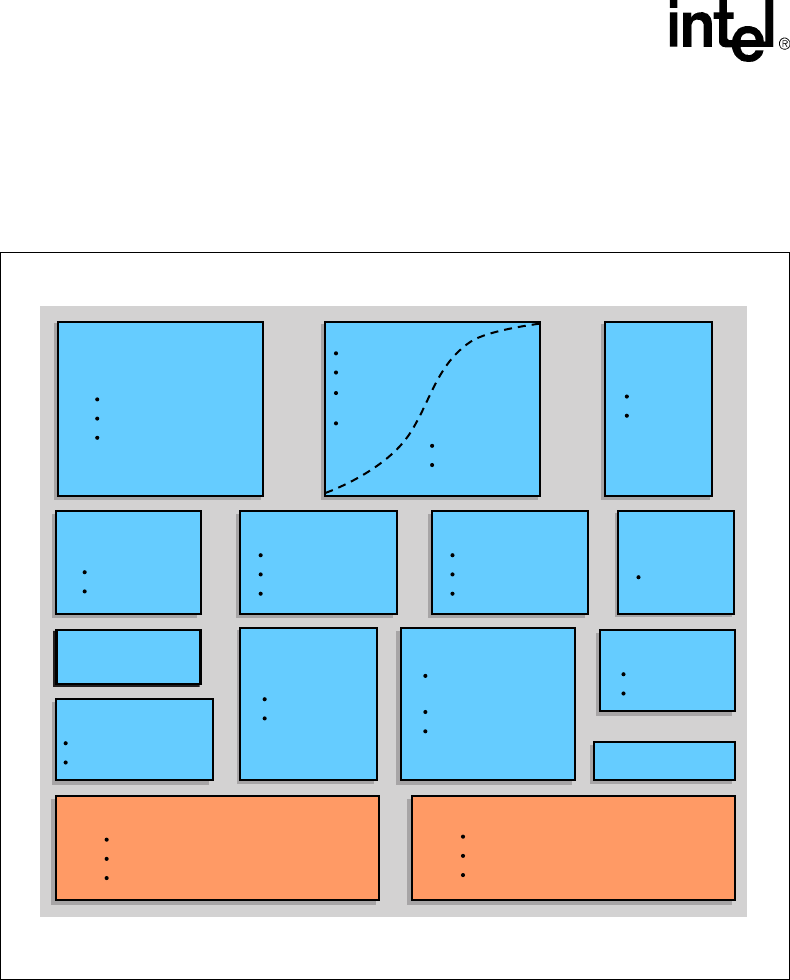

Figure 1-1 shows the major functional blocks of the Intel

®

80200 processor. The following

sections give a brief, high-level overview of these blocks.

1.1.2.1 Multiply/Accumulate (MAC)

The MAC unit supports early termination of multiplies/accumulates in two cycles and can sustain a

throughput of a MAC operation every cycle. Several architectural enhancements were made to the

MAC to support audio coding algorithms, which include a 40-bit accumulator and support for

16-bit packed data.

See Section 2.3, “Extensions to ARM* Architecture” on page 2-3 for more details.

Figure 1-1. Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture Features

B1307-01

Instruction

Cache

32 Kbytes

32 ways

Lockable by line

Interrupt Controller

Interrupt Masking

FIQ/IRQ Steering

Pend Register

Bus Controller

1 Gbyte/sec

Pipelined, de-multiplexed

ECC protection

Mini-Data

Cache

2 Kbytes

2 ways

Branch Target

Buffer

2 Kbytes

2 ways

Debug

Hardware Breakpoint

Branch History Table

Power

Management

Idle

Sleep

MAC

Single Cycle

Throughput (16*32)

16-bit SIMD

40-bit Accumulator

Performance

Monitoring

Write Buffer

8 entries

Full coalescing

JTAG

IMMU

32 entry TLB

Fully associative

Lockable by entry

DMMU

32 entry TLB

Fully associative

Lockable by entry

Fill

Buffer

4 - 8 entries

Data Cache

Max 32 Kbytes

32 ways

wr-back or

wr-through

Hit under

miss

Data RAM

Max 28 Kbytes

Re-map of

data cache