Developer’s Manual March, 2003 14-7

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Considerations

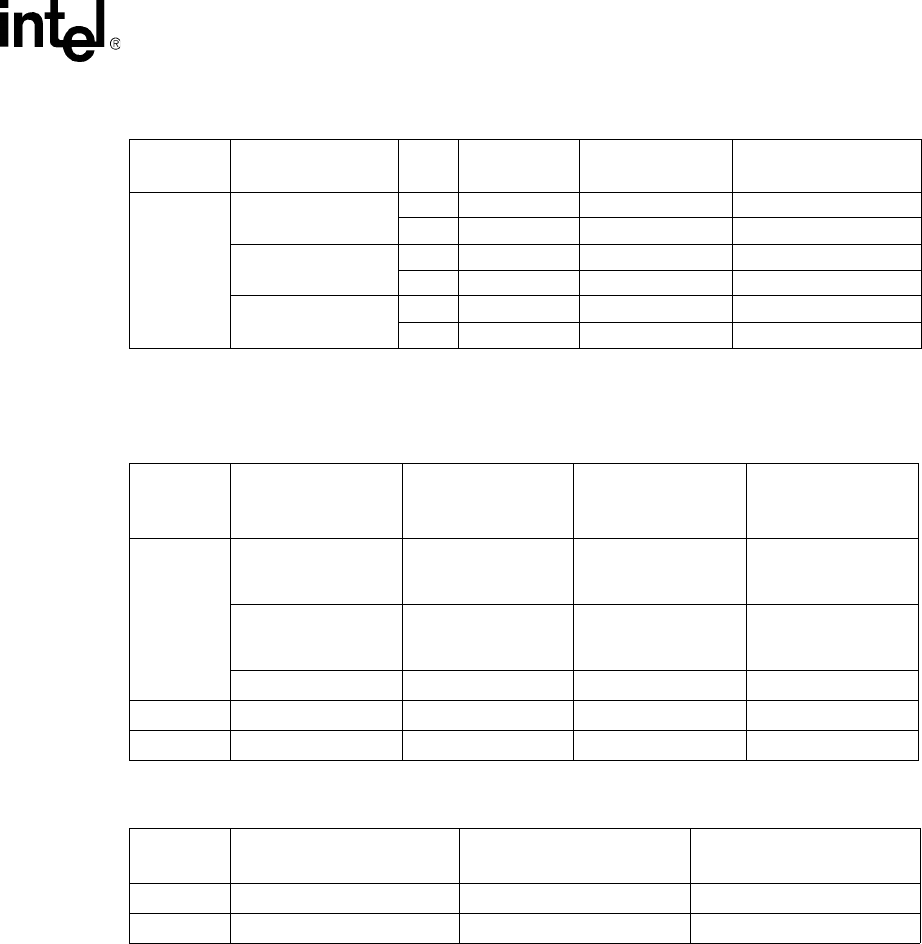

UMULL

Rs[31:15] = 0x00000

0 1 RdLo = 2; RdHi = 3 2

13 3 3

Rs[31:27] = 0x00

0 1 RdLo = 3; RdHi = 4 3

14 4 4

all others

0 1 RdLo = 4; RdHi = 5 4

15 5 5

1. If the next instruction needs to use the result of the multiply for a shift by immediate or as Rn in a QDADD or QDSUB, one

extra cycle of result latency is added to the number listed.

Table 14-8. Multiply Implicit Accumulate Instruction Timings

Mnemonic

Rs Value (Early

Termination)

Minimum Issue

Latency

Minimum Result

Latency

Minimum Resource

Latency

(Throughput)

MIA

Rs[31:16] = 0x0000

or

Rs[31:16] = 0xFFFF

111

Rs[31:28] = 0x0

or

Rs[31:28] = 0xF

122

all others 1 3 3

MIAxyN/A111

MIAPHN/A122

Table 14-9. Implicit Accumulator Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

Minimum Resource Latency

(Throughput)

MAR222

MRA 1 (RdLo = 2; RdHi = 3)

1

1. If the next instruction needs to use the result of the MRA for a shift by immediate or as Rn in a QDADD or QDSUB, one extra

cycle of result latency is added to the number listed.

2

Table 14-7. Multiply Instruction Timings (Sheet 2 of 2)

Mnemonic

Rs Value

(Early Termination)

S-Bit

Value

Minimum

Issue Latency

Minimum Result

Latency

1

Minimum Resource

Latency (Throughput)