Developer’s Manual March, 2003 10-17

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

10.3.4 Word Write

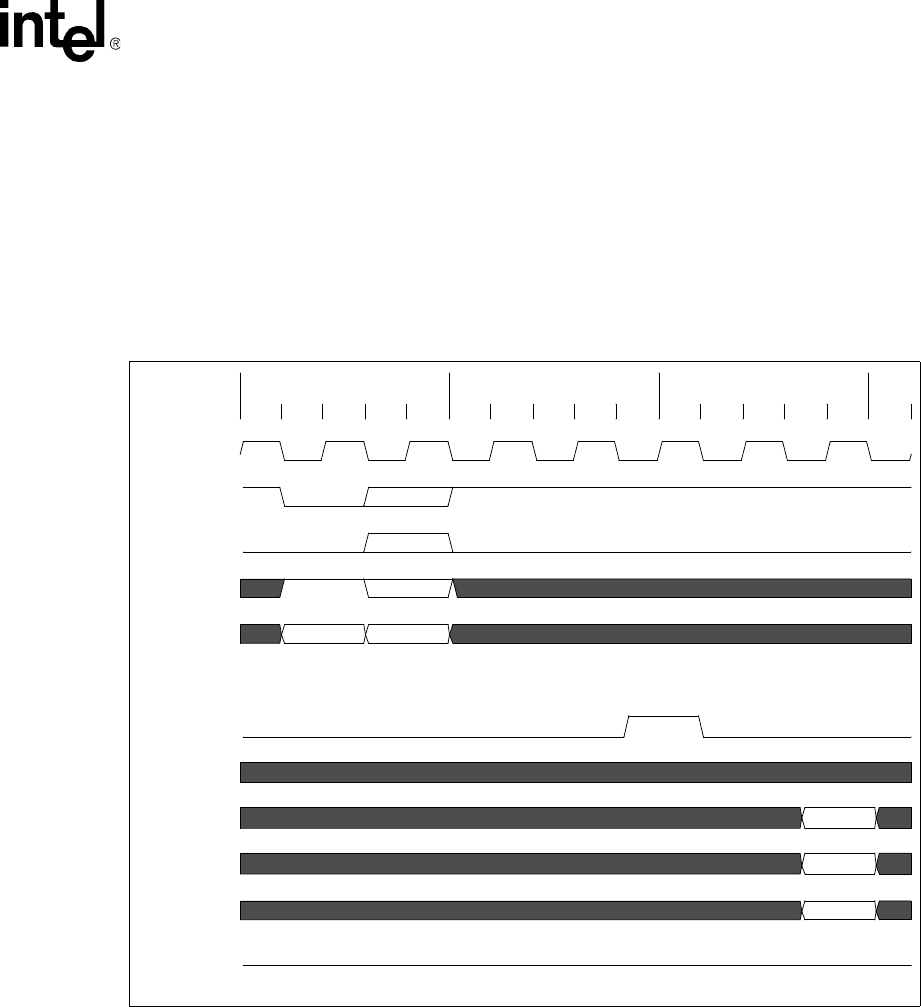

Figure 10-7 shows a 32-bit write request to address 0x240. W/R# is high when ADS# is asserted

low. Two cycles before the write data needs to be on the bus for the SDRAM, DValid is asserted

by the chipset to the Intel

®

80200 processor to tell the Intel

®

80200 processor the data is needed.

Two cycles later the Intel

®

80200 processor drives the data onto the D bus (the lower 32 bits in this

case) along with the appropriate check bits and byte enables. In this case the low four byte enables

are asserted (low) and the upper four are deasserted (high) because the write data is on the low four

bytes of the bus.

Figure 10-7. Basic Word Write

Wr Req

0x240

WrData

0xF0

ECC

0x0

0

1

0

0ns 25ns 50ns 75ns

MCLK

ADS#/LEN[2]

Lock/LEN[1]

W/R#/LEN[0]

A

DValid

CWF

D

BEn

DCB

Abort