13-4 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.4.1 Global Enable Bit (GE)

The Global Enable bit disables and enables all debug functionality (except the reset vector trap).

Following a processor reset, this bit is clear so all debug functionality is disabled. When debug

functionality is disabled, the BKPT instruction becomes a noop and external debug breaks,

hardware breakpoints, and non-reset vector traps are ignored.

13.4.2 Halt Mode Bit (H)

The Halt Mode bit configures the debug unit for either halt mode or monitor mode.

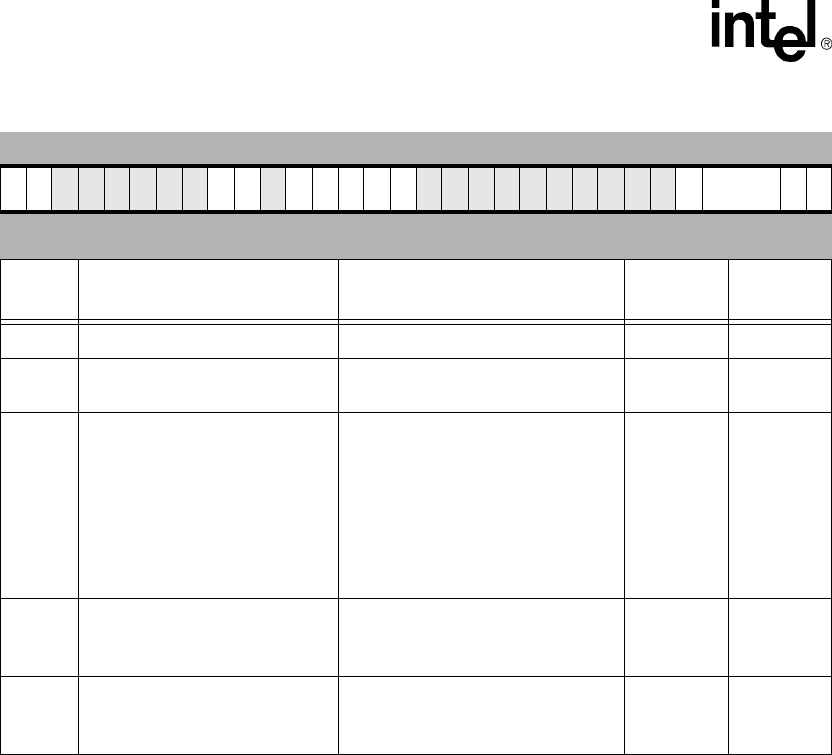

15:6 Read-undefined / Write-As-Zero Reserved undefined undefined

5

SW Read / Write

JTAG Read-Only

Sticky Abort (SA)

0 unchanged

4:2

SW Read / Write

JTAG Read-Only

Method Of Entry (MOE)

000: Processor Reset

001: Instruction Breakpoint Hit

010: Data Breakpoint Hit

011: BKPT Instruction Executed

100: External Debug Event Asserted

101: Vector Trap Occurred

110: Trace Buffer Full Break

111: Reserved

0b000 unchanged

1

SW Read / Write

JTAG Read-Only

Trace Buffer Mode (M)

0: Wrap around mode

1: fill-once mode

0 unchanged

0

SW Read / Write

JTAG Read-Only

Trace Buffer Enable (E)

0: Disabled

1: Enabled

0 unchanged

Table 13-1. Debug Control and Status Register (DCSR) (Sheet 2 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

GE H TF TI TD TATS TUTR SA MOE M E

Bits Access Description

Reset

Value

TRST

Value