Developer’s Manual March, 2003 10-7

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

10.2.3 Critical Word First

The CWF signal is only used during read bursts of eight words (Len = 6). CWF needs to be driven

at the same time as DValid of the first data cycle of the transaction. This bit indicates to the

requesting master what order the data is returning in. The Intel

®

80200 processor uses this sort of

transaction to fill a cache line.

There are two acceptable return orders that may be signalled with CWF:

• (CWF = 0) starting with the words 0 and 1 (64-bit bus) or word 0 (32-bit bus) and sequentially

returning the data

• (CWF = 1) returning the word or pair of words that contain the byte indicated by the request

address on the first cycle, sequentially returning the next highest memory location word or pair

of words until the end of the eight word aligned block, then returning the lowest word or pair

of words and incrementing back up the word or pair of words just below the word or pair of

words pointed to by the request address.

The allowable orders are spelled out below. In this description, A,B,C, and D refer to pairs of 32-bit

words in the aligned 8-word block (A=0,1 B=2,3 C=4,5 D=6,7). In the 32-bit bus section, a-h are

referring to the eight words in the aligned 8-word block. Note that the Intel

®

80200 processor will

align all 8-word burst transactions on a 64-bit address. Specifically, if the instruction or data

address requested by the program is odd word aligned, the Intel

®

80200 processor will emit a

64-bit aligned address by setting A[2] = 0x0.

1. The Intel® 80200 processor will never generate an 8-word burst with A[2] = 0x1. The addresses for these requests will be 64-bit

aligned.

The timing of write transactions on the data bus is similar to the timing of reads. After a write

request has gone out, two cycles before the chipset or memory is ready to receive the data from the

Intel

®

80200 processor the DValid is asserted. Two cycles later the Intel

®

80200 processor drives

the data onto the data bus. For a write whose data all fits within one aligned 64-bit memory block

(for a 64-bit bus) or a 32-bit aligned memory block (for a 32-bit bus) there is a single data cycle.

For a burst write, there can be up to two (64-bit bus) or four (32-bit bus) data cycles, for a

maximum write burst of four 32-bit words.

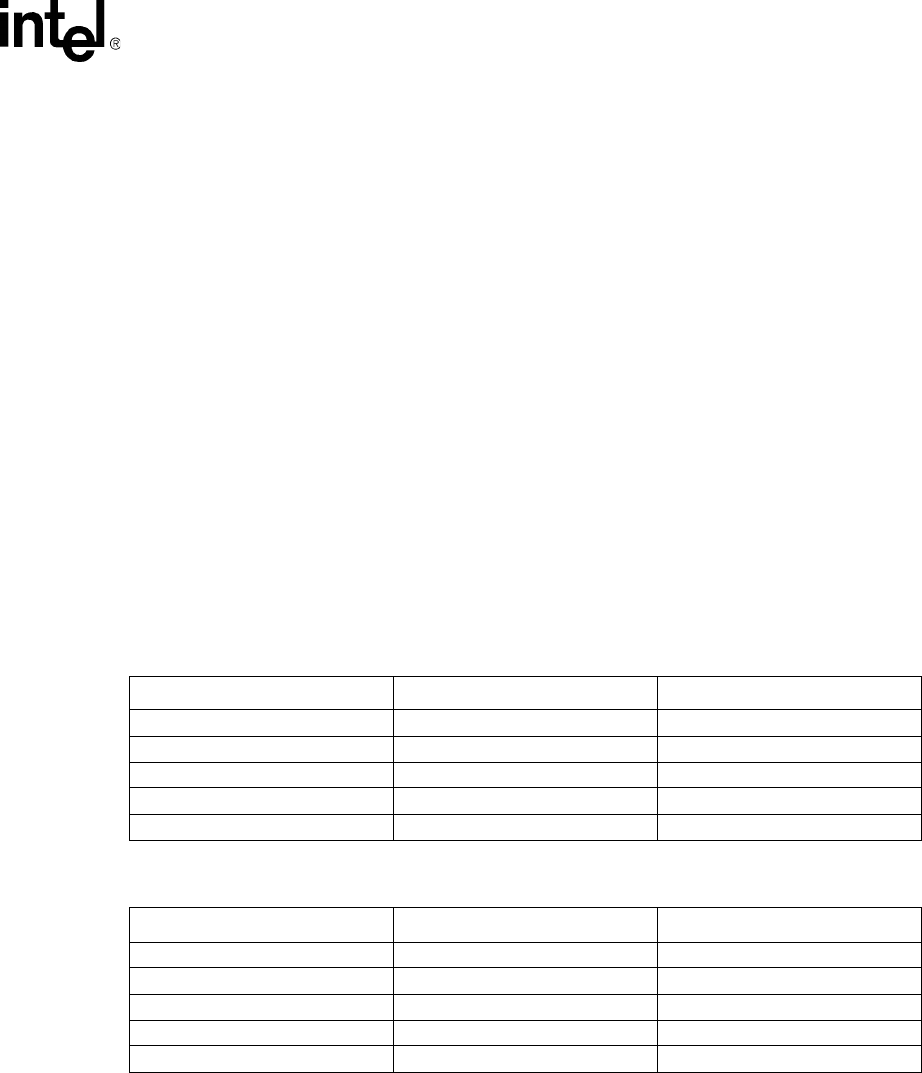

Table 10-4. Return Order for 8-Word Burst, 64-bit Data Bus

CWF A[4:3] Return Order

0XXABCD

100ABCD

1 01 BCDA

1 10 CDAB

111DABC

Table 10-5. Return Order for 8-Word Burst, 32-bit Data Bus

CWF A[4:2]

1

Return Order

0 XXX abcdefgh

1 000 abcdefgh

1 010 cdefghab

1 100 efghabcd

1 110 ghabcdef