Developer’s Manual March, 2003 13-15

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.8.4 TX Register Ready Bit (TR)

The debugger and debug handler use the TR bit to synchronize accesses to the TX register. The

debugger and debug handler must poll the TR bit before accessing the TX register. Table 13-9

shows the handshaking used to access the TX register.

13.8.5 Conditional Execution Using TXRXCTRL

All of the bits in TXRXCTRL are placed such that they can be read directly into the CC flags using

an MCR instruction. To simplify the debug handler, the TXRXCTRL register should be read using

the following instruction:

mrc p14, 0, r15, C14, C0, 0

This instruction directly updates the condition codes in the CPSR. The debug handler can then

conditionally execute based on each CC bit. Table 13-10 shows the mnemonic extension to

conditionally execute based on whether the TXRXCTRL bit is set or clear.

The following example is a code sequence in which the debug handler polls the TXRXCTRL

handshaking bit to determine when the debugger has completed its write to RX and the data is

ready for the debug handler to read.

loop: mrc p14, 0, r15, c14, c0, 0# read the handshaking bit in TXRXCTRL

mcrmi p14, 0, r0, c9, c0, 0 # if RX is valid, read it

bpl loop # if RX is not valid, loop

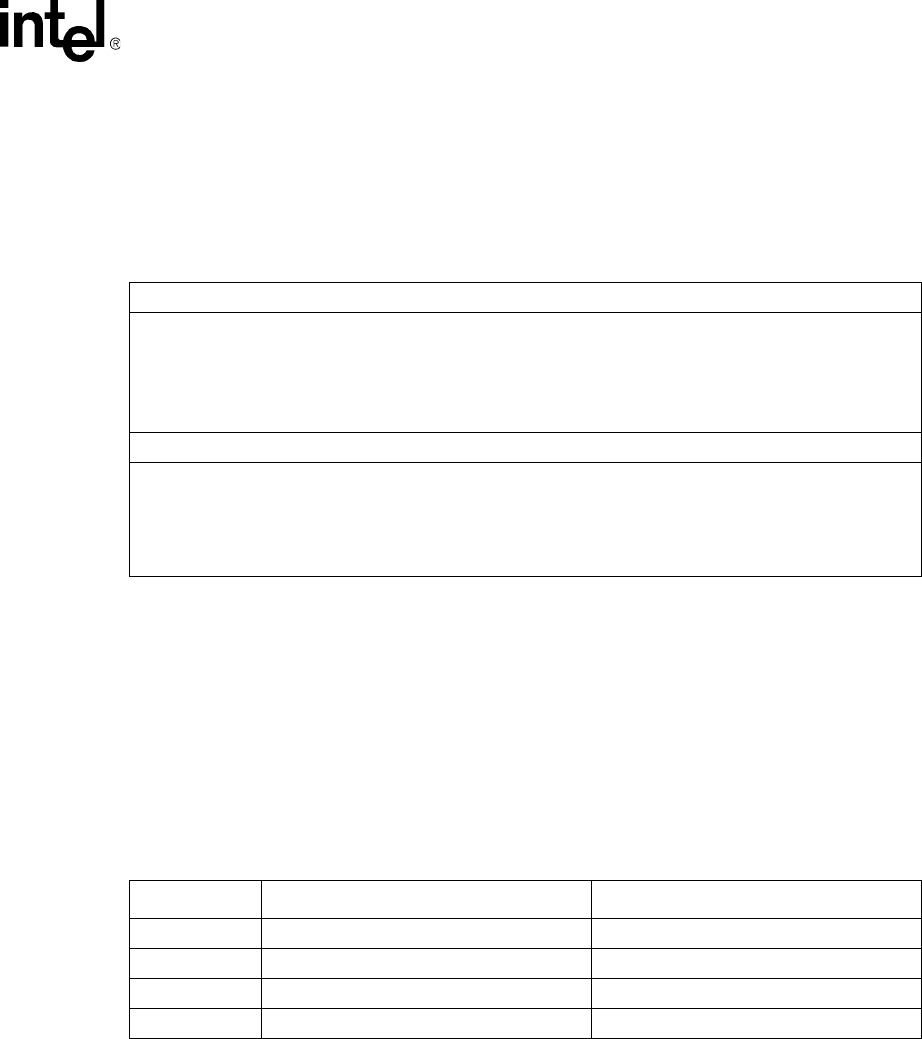

Table 13-9. TX Handshaking

Debugger Actions

Debugger is expecting data from the debug handler.

Before reading data from the TX register, the debugger polls the TR bit through JTAG until the bit is set. NOTE:

while polling TR, the debugger must scan out the TR bit and the TX register data.

Reading a ‘1’ from the TR bit, indicates that the TX data scanned out is valid

The action of scanning out data when the TR bit is set, automatically clears TR.

Debug Handler Actions

Debug handler wants to send data to the debugger (in response to a previous request).

The debug handler polls the TR bit to determine when the TX register is empty (any previous data has been

read out by the debugger). The handler polls the TR bit until it is clear.

Once the TR bit is clear, the debug handler writes new data to the TX register. The write operation

automatically sets the TR bit.

Table 13-10. TXRXCTRL Mnemonic Extensions

TXRXCTRL bit mnemonic extension to execute if bit set mnemonic extension to execute if bit clear

31 (to N flag) MI PL

30 (to Z flag) EQ NE

29 (to C flag) CS CC

28 (to V flag) VS VC