7-8 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

The mini-data cache attribute bits, in the Intel

®

80200 processor Control Register, are used to

control the allocation policy for the mini-data cache and whether it uses write-back caching or

write-through caching.

The configuration of the mini-data cache should be setup before any data access is made that may

be cached in the mini-data cache. Once data is cached, software must ensure that the mini-data

cache has been cleaned and invalidated before the mini-data cache attributes can be changed.

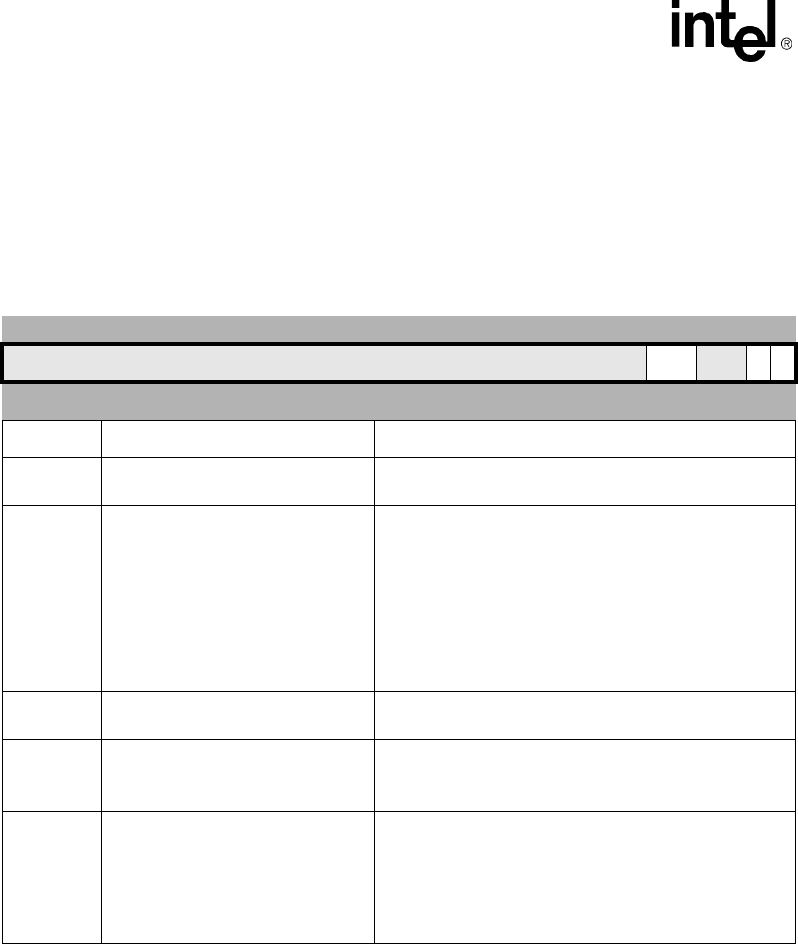

Table 7-7. Auxiliary Control Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MD PK

reset value: writeable bits set to 0

Bits Access Description

31:6

Read-Unpredictable /

Write-as-Zero

Reserved

5:4 Read / Write

Mini Data Cache Attributes (MD)

All configurations of the Mini-data cache are cacheable,

stores are buffered in the write buffer and stores are

coalesced in the write buffer as long as coalescing is

globally enabled (bit 0 of this register).

0b00 = Write back, Read allocate

0b01 = Write back, Read/Write allocate

0b10 = Write through, Read allocate

0b11 = Unpredictable

3:2

Read-Unpredictable /

Write-as-Zero

Reserved

1 Read / Write

Page Table Memory Attribute (P)

If set, page table accesses are protected by ECC. See

Chapter 11, “Bus Controller” for more information.

0 Read / Write

Write Buffer Coalescing Disable (K)

This bit globally disables the coalescing of all stores in the

write buffer no matter what the value of the Cacheable

and Bufferable bits are in the page table descriptors.

0 = Enabled

1 = Disabled