2-10 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

The P bit controls ECC.

The TEX (Type Extension) field is present in several of the descriptor types. In the Intel

®

80200

processor, only the LSB of this field is used; this is called the X bit.

A Small Page descriptor does not have a TEX field. For these descriptors, TEX is implicitly zero;

that is, they operate as if the X bit had a ‘0’ value.

The X bit, when set, modifies the meaning of the C and B bits. Description of page attributes and

their encoding can be found in Chapter 3, “Memory Management”.

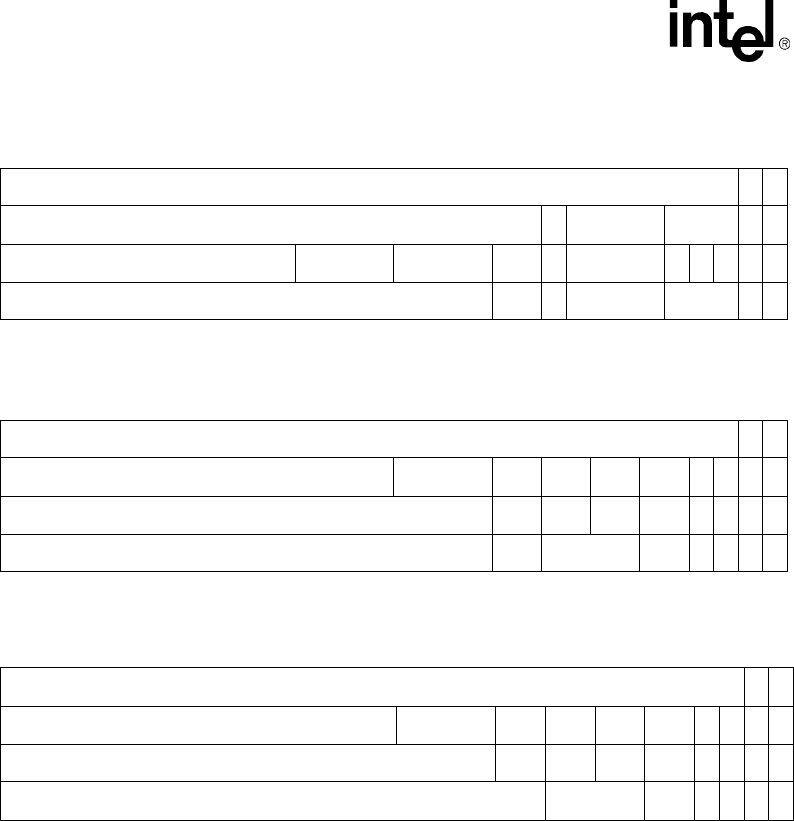

Table 2-8. First-level Descriptors

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SBZ 0 0

Coarse page table base address P Domain SBZ 0 1

Section base address SBZ TEX AP P Domain 0 C B 1 0

Fine page table base address SBZ P Domain SBZ 1 1

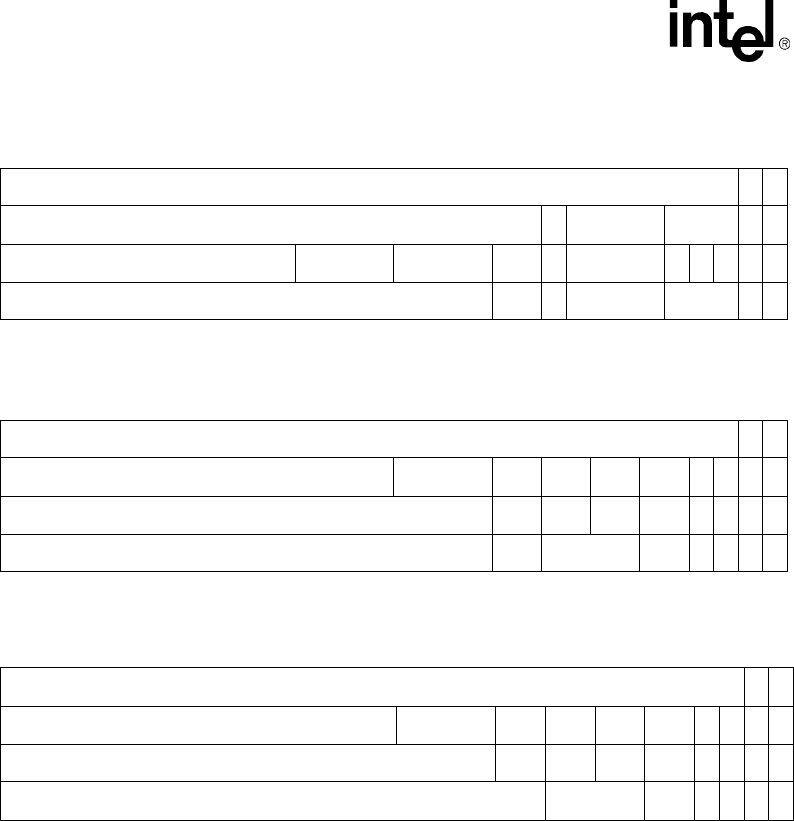

Table 2-9. Second-level Descriptors for Coarse Page Table

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SBZ 0 0

Large page base address TEX AP3 AP2 AP1 AP0 C B 0 1

Small page base address AP3 AP2 AP1 AP0 C B 1 0

Extended small page base address SBZ TEX AP C B 1 1

Table 2-10. Second-level Descriptors for Fine Page Table

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SBZ 0 0

Large page base address TEX AP3 AP2 AP1 AP0 C B 0 1

Small page base address AP3 AP2 AP1 AP0 C B 1 0

Tiny Page Base Address TEX AP C B 1 1