2-6 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

The MIAxy instruction performs one16-bit signed multiply and accumulates these to a single

40-bit accumulator. x refers to either the upper half or lower half of register Rm (multiplicand) and

y refers to the upper or lower half of Rs (multiplier). A value of 0x1 selects bits [31:16] of the

register which is specified in the mnemonic as T (for top). A value of 0x0 selects bits [15:0] of the

register which is specified in the mnemonic as B (for bottom).

MIAxy does not support unsigned multiplication; all values in Rs and Rm are interpreted as signed

data values.

The instruction is only executed if the condition specified in the instruction matches the condition

code status.

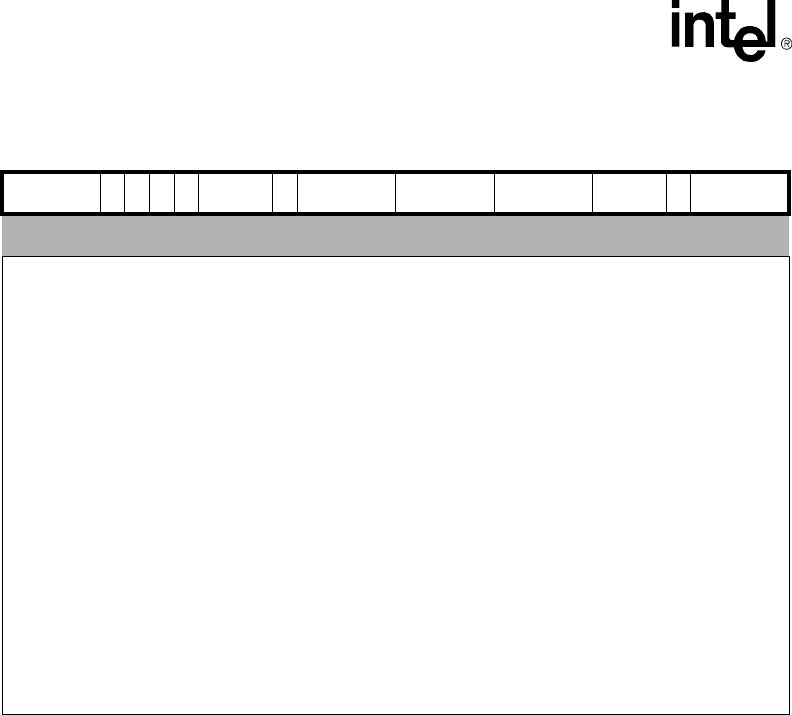

Table 2-4. MIAxy{<cond>} acc0, Rm, Rs

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1110001011xy Rs 00000001 Rm

Operation: if ConditionPassed(<cond>) then

if (bit[17] == 0)

<operand1> = Rm[15:0]

else

<operand1> = Rm[31:16]

if (bit[16] == 0)

<operand2> = Rs[15:0]

else

<operand2> = Rs[31:16]

acc0[39:0] = sign_extend(<operand1> * <operand2>) + acc0[39:0]

Exceptions:none

Qualifiers Condition Code

S bit is always cleared; no condition code flags are updated

Notes: Instruction timings can be found

in Section 14.4.4, “Multiply Instruction Timings” on page 14-6.

Specifying R15 for register Rs or Rm has unpredictable results.

acc0 is defined to be 0b000 on 80200.