Developer’s Manual March, 2003 7-11

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

7.2.8 Register 7: Cache Functions

All the functions defined in the first generation of Intel

®

StrongARM* appear here. The Intel

®

80200 processor adds other functions as well. This register should be accessed as write-only. Reads

from this register, as with an MRC, have an undefined effect.

The Drain Write Buffer function not only drains the write buffer but also drains the fill buffer.

The Intel

®

80200 processor does not check permissions on addresses supplied for cache or TLB

functions. Because only privileged software may execute these functions, full accessibility is

assumed. Cache functions do not generate any of the following:

• translation faults

• domain faults

• permission faults

The invalidate instruction cache line command does not invalidate the BTB. If software invalidates

a line from the instruction cache and modifies the same location in external memory, it needs to

invalidate the BTB also. Not invalidating the BTB in this case may cause unpredictable results.

Disabling/enabling a cache has no effect on contents of the cache: valid data stays valid, locked

items remain locked. All operations defined in Table 7-12 work regardless of whether the cache is

enabled or disabled.

Since the Clean D Cache Line function reads from the data cache, it is capable of generating a

parity fault. The other operations do not generate parity faults.

The line-allocate command allocates a tag into the data cache specified by bits [31:5] of Rd. If a

valid dirty line (with a different MVA) already exists at this location, it will be evicted. The 32

bytes of data associated with the newly allocated line are not initialized and therefore generates

unpredictable results if read.

This command may be used for cleaning the entire data cache on a context switch and also when

re-configuring portions of the data cache as data RAM. In both cases, Rd is a virtual address that

maps to some non-existent physical memory. When creating data RAM, software must initialize

the data RAM before read accesses can occur. Specific uses of these commands can be found in

Chapter 6, “Data Cache”.

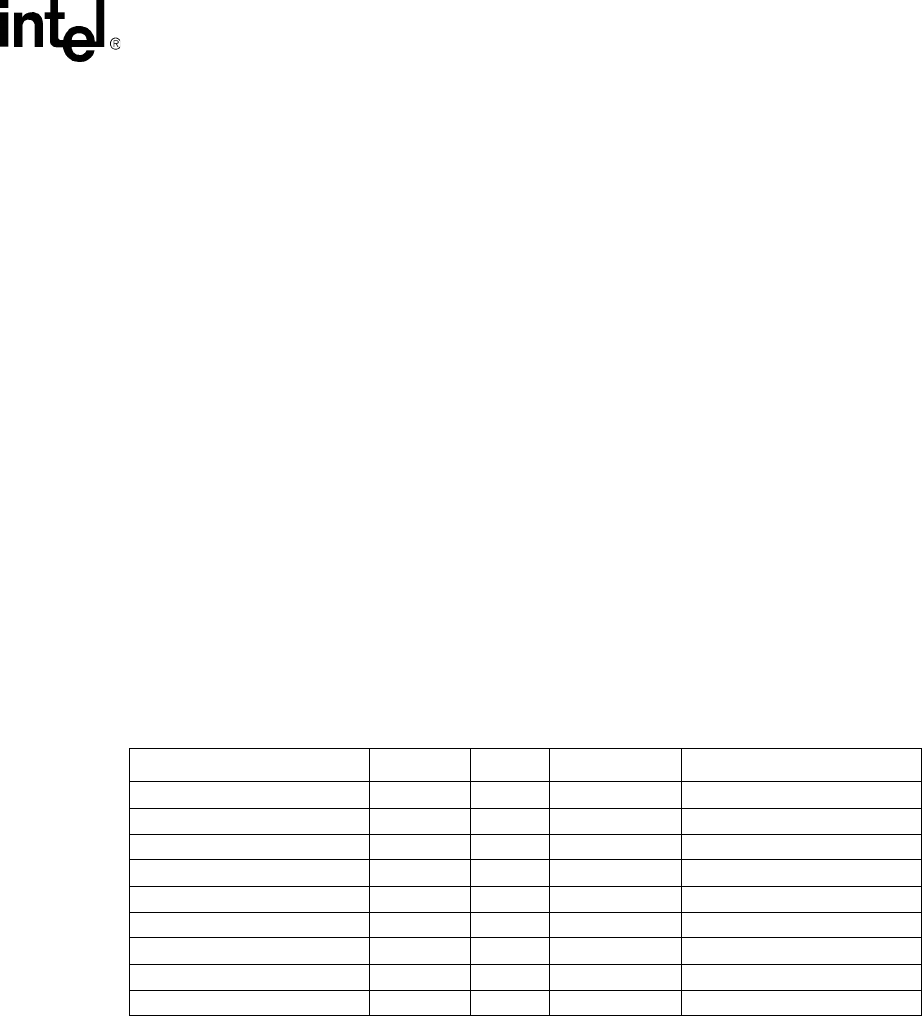

Table 7-12. Cache Functions

Function opcode_2 CRm Data Instruction

Invalidate I&D cache & BTB 0b000 0b0111 Ignored MCR p15, 0, Rd, c7, c7, 0

Invalidate I cache & BTB 0b000 0b0101 Ignored MCR p15, 0, Rd, c7, c5, 0

Invalidate I cache line 0b001 0b0101 MVA MCR p15, 0, Rd, c7, c5, 1

Invalidate D cache 0b000 0b0110 Ignored MCR p15, 0, Rd, c7, c6, 0

Invalidate D cache line 0b001 0b0110 MVA MCR p15, 0, Rd, c7, c6, 1

Clean D cache line 0b001 0b1010 MVA MCR p15, 0, Rd, c7, c10, 1

Drain Write (& Fill) Buffer 0b100 0b1010 Ignored MCR p15, 0, Rd, c7, c10, 4

Invalidate Branch Target Buffer 0b110 0b0101 Ignored MCR p15, 0, Rd, c7, c5, 6

Allocate Line in the Data Cache 0b101 0b0010 MVA MCR p15, 0, Rd, c7, c2, 5