Developer’s Manual March, 2003 2-13

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

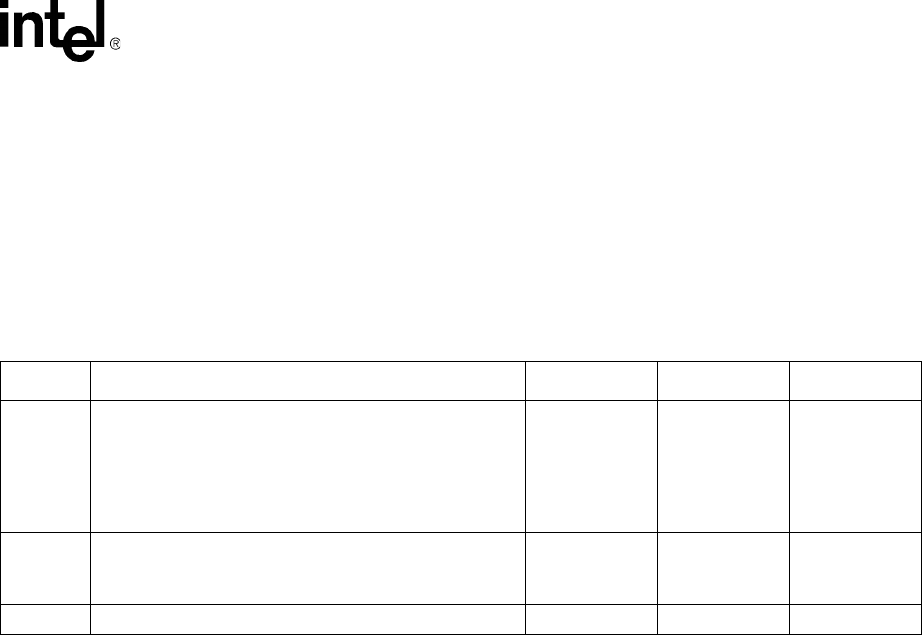

2.3.4.3 Prefetch Aborts

The Intel

®

80200 processor detects three types of prefetch aborts: Instruction MMU abort, external

abort on an instruction access, and an instruction cache parity error. These aborts are described in

Table 2-13.

When a prefetch abort occurs, hardware reports the highest priority one in the extended Status field

of the Fault Status Register. The value placed in R14_ABORT (the link register in abort mode) is

the address of the aborted instruction + 4.

Table 2-13. Intel

®

80200 Processor Encoding of Fault Status for Prefetch Aborts

Priority Sources FS[10,3:0]

a

a. All other encodings not listed in the table are reserved.

Domain FAR

Highest

Instruction MMU Exception

Several exceptions can generate this encoding:

- translation faults

- domain faults, and

- permission faults

It is up to software to figure out which one occurred.

0b10000 invalid invalid

External Instruction Error Exception

This exception occurs when the external memory system

reports an error on an instruction cache fetch.

0b10110 invalid invalid

Lowest Instruction Cache Parity Error Exception 0b11000 invalid invalid