8-2 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

System Management

The Intel

®

80200 processor supports low voltage operation with a supply as low as 0.95 V. At

lower voltages, not all CCLK configurations are available. See the Intel

®

80200 processor

Datasheet for voltage/frequency information.

Changing CCLK frequency is similar to entering a low power mode. First, the core is stalled

waiting for all processing to complete, second the new configuration is programmed into

CCLKCFG, and then finally the core waits for the PLL to re-lock. The exact code sequence is

shown in Equation 8-1. If there are no external bus transactions, this procedure takes

approximately two thousand CLK cycles, the same time it takes to transition out of reset.

After the Intel

®

80200 processor resets, the value in CCLKCFG reflects the effect of the PLLCFG

pin: CCLKCFG contains either one or four.

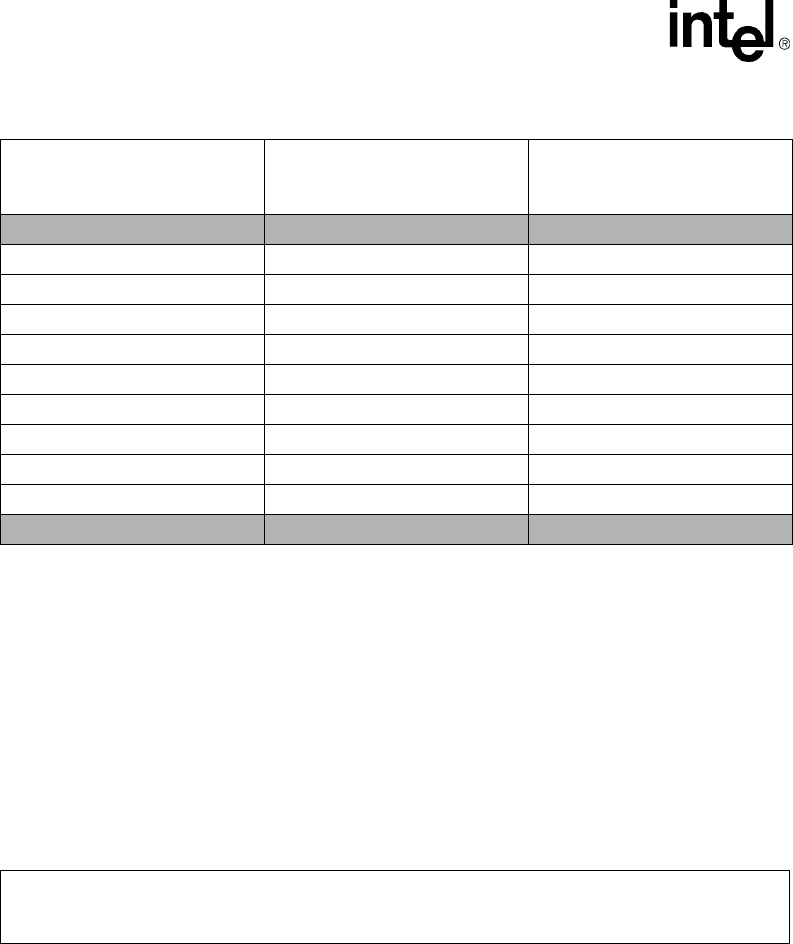

Table 8-2. Software CCLK Configuration

CCLKCFG[3:0]

(Coprocessor 14, register 6)

Multiplier for CLK

Example: CCLK Frequency

(MHZ), assuming CLK

Frequency of 66MHz

0 (reserved) Unpredictable

1 3 200

2 4 266

3 5 333

4 6 400

5 7 466

6 8 533

7 9 600

8 10 666

9 11 733

10-15 (reserved) Unpredictable

Example 8-1. CCLK Modification Procedure

MOV R1, #7; New CCLKCFG value

MCR P14,0,R1,C6,C0,0; Change core clock frequency and wait for PLL

; to re-lock