7-14 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

7.2.10 Register 9: Cache Lock Down

Register 9 is used for locking down entries into the instruction cache and data cache. (The protocol

for locking down entries can be found in Chapter 6, “Data Cache”.)

Table 7-14 shows the command for locking down entries in the instruction cache, instruction TLB,

and data TLB. The entry to lock is specified by the virtual address in Rd. The data cache locking

mechanism follows a different procedure than the others. The data cache is placed in lock down

mode such that all subsequent fills to the data cache result in that line being locked in, as controlled

by Table 7-15.

Lock/unlock operations on a disabled cache have an undefined effect. This register should be

accessed as write-only. Reads from this register, as with an MRC, have an undefined effect.

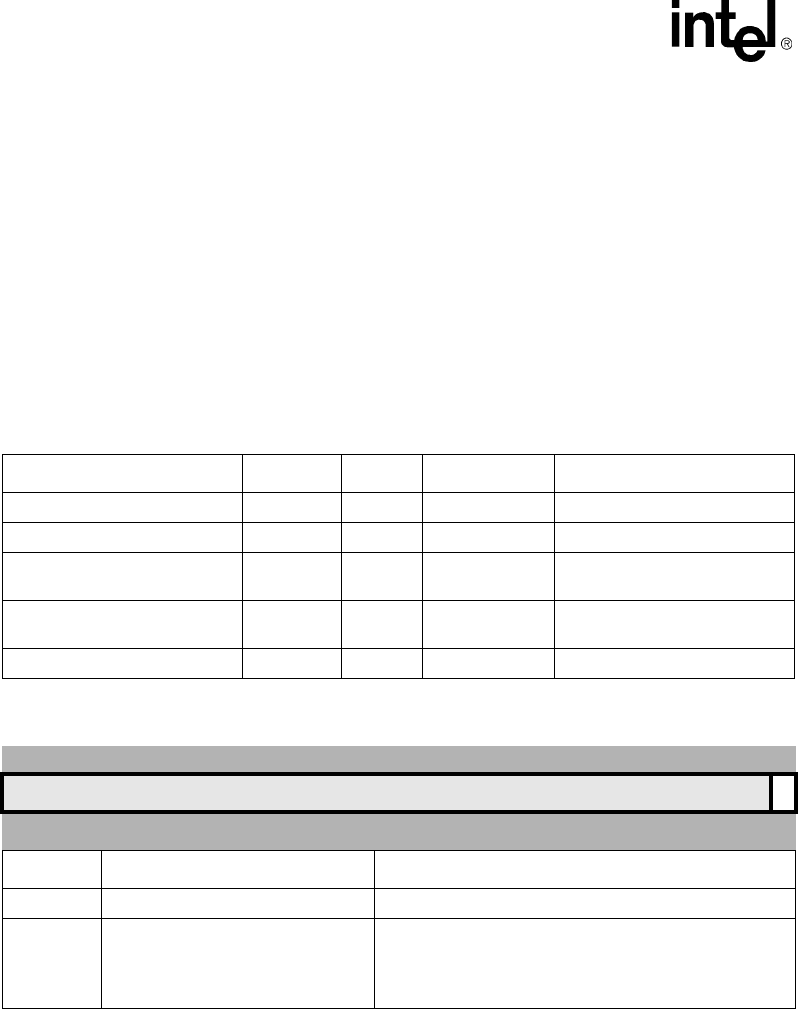

Table 7-14. Cache Lockdown Functions

Function opcode_2 CRm Data Instruction

Fetch and Lock I cache line 0b000 0b0001 MVA MCR p15, 0, Rd, c9, c1, 0

Unlock Instruction cache 0b001 0b0001 Ignored MCR p15, 0, Rd, c9, c1, 1

Read data cache lock register 0b000 0b0010

Read lock mode

value

MRC p15, 0, Rd, c9, c2, 0

Write data cache lock register 0b000 0b0010

Set/Clear lock

mode

MCR p15, 0, Rd, c9, c2, 0

Unlock Data Cache 0b001 0b0010 Ignored MCR p15, 0, Rd, c9, c2, 1

Table 7-15. Data Cache Lock Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

L

reset value: writeable bits set to 0

Bits Access Description

31:1 Read-unpredictable / Write-as-Zero Reserved

0 Read-unpredictable / Write

Data Cache Lock Mode (L)

0 = No locking occurs

1 = Any fill into the data cache while this bit is set gets

locked in