Developer’s Manual March, 2003 7-17

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

7.2.14 Register 14: Breakpoint Registers

The Intel

®

80200 processor contains two instruction breakpoint address registers (IBCR0 and

IBCR1), one data breakpoint address register (DBR0), one configurable data mask/address register

(DBR1), and one data breakpoint control register (DBCON). The Intel

®

80200 processor also

supports a 256 entry, trace buffer that records program execution information. The registers to

control the trace buffer are located in CP14.

Refer to Chapter 13, “Software Debug” for more information on these features of the Intel

®

80200

processor.

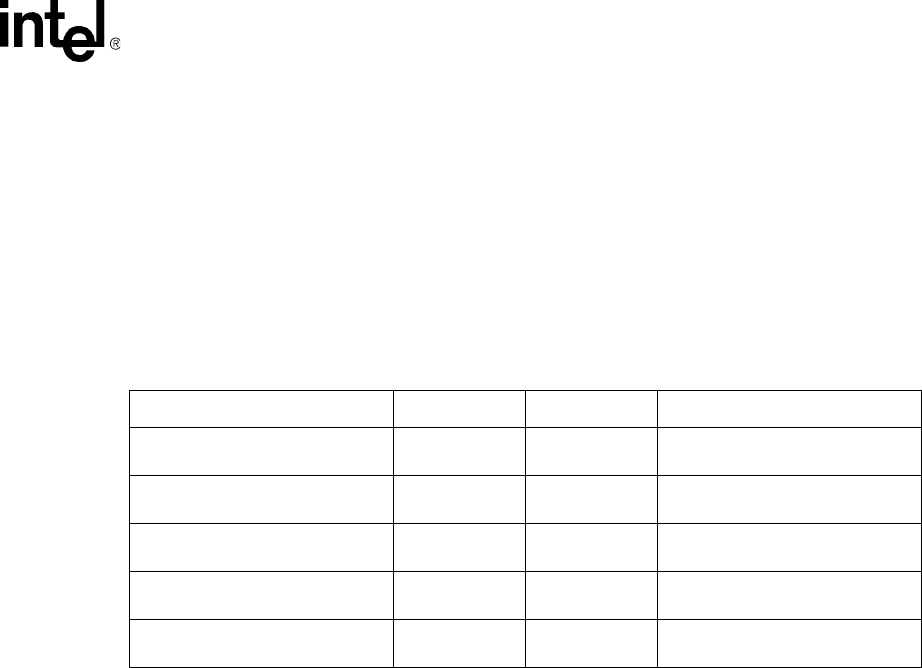

Table 7-19. Accessing the Debug Registers

Function opcode_2 CRm Instruction

Access Instruction Breakpoint

Control Register 0 (IBCR0)

0b000 0b1000

MRC p15, 0, Rd, c14, c8, 0 ; read

MCR p15, 0, Rd, c14, c8, 0 ; write

Access Instruction Breakpoint

Control Register 1(IBCR1)

0b000 0b1001

MRC p15, 0, Rd, c14, c9, 0 ; read

MCR p15, 0, Rd, c14, c9, 0 ; write

Access Data Breakpoint Address

Register (DBR0)

0b000 0b0000

MRC p15, 0, Rd, c14, c0, 0 ; read

MCR p15, 0, Rd, c14, c0, 0 ; write

Access Data Mask/Address

Register (DBR1)

0b000 0b0011

MRC p15, 0, Rd, c14, c3, 0 ; read

MCR p15, 0, Rd, c14, c3, 0 ; write

Access Data Breakpoint Control

Register (DBCON)

0b000 0b0100

MRC p15, 0, Rd, c14, c4, 0 ; read

MCR p15, 0, Rd, c14, c4, 0 ; write