Developer’s Manual March, 2003 7-5

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

7.2.1 Register 0: ID and Cache Type Registers

Register 0 houses two read-only registers that are used for part identification: an ID register and a

cache type register.

The ID Register is selected when opcode_2=0. This register returns the code for the Intel

®

80200

processor: 0x69052000 for A0 stepping/revision. The low order four bits of the register are the chip

revision number and will be incremented for future steppings.

The Cache Type Register is selected when opcode_2=1 and describes the present Intel

®

80200

processor cache.

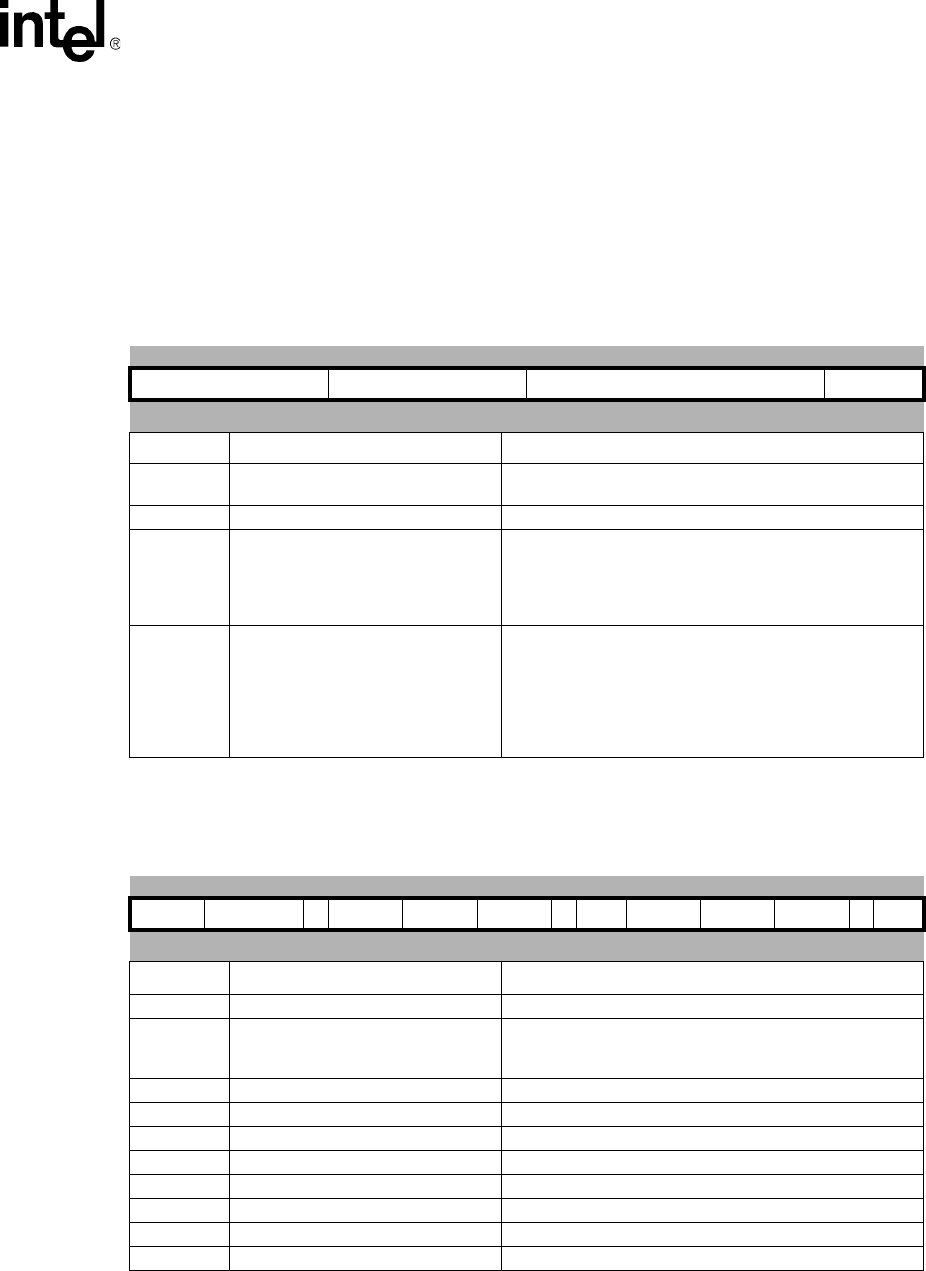

Table 7-4. ID Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0110100100000101001000000000 Revision

reset value: As Shown

Bits Access Description

31:24 Read / Write Ignored

Implementation trademark

(0x69 = ‘i’= Intel Corporation)

23:16 Read / Write Ignored Architecture version = ARM* Version 5

15:4 Read / Write Ignored

Part Number (Implementation Specified)

Intel

®

80200 processor: 0x200

Bits[15:12] refer to the processor generation.

Bits[11:8] refer to the implementation

Bits[7:4] used for implementation derivatives

3:0 Read / Write Ignored

Revision number for the processor (Implementation

Specified)

A0 stepping = 0b0000

A1 stepping = 0b0001

B0 stepping = 0b0010

C0 stepping = 0b0011

D0 stepping = 0b0100

Table 7-5. Cache Type Register (Sheet 1 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

00001011000110101010000110101010

reset value: As Shown

Bits Access Description

31:29 Read-as-Zero / Write Ignored Reserved

28:25 Read / Write Ignored

Cache class = 0b0101

The caches support locking, write back and round-robin

replacement. They do not support address by index.

24 Read / Write Ignored Harvard Cache

23:21 Read-as-Zero / Write Ignored Reserved

20:18 Read / Write Ignored Data Cache Size = 0b110 = 32 kB

17:15 Read / Write Ignored Data cache associativity = 0b101 = 32

14 Read-as-Zero / Write Ignored Reserved

13:12 Read / Write Ignored Data cache line length = 0b10 = 8 words/line

11:9 Read-as-Zero / Write Ignored Reserved

8:6 Read / Write Ignored Instruction cache size = 0b110 = 32 kB