Developer’s Manual March, 2003 10-13

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

External Bus

10.2.8 Big Endian System Configuration

The Intel

®

80200 processor supports execution in a big endian system. A system is said to be big

endian if multi-byte values are accessed with the MSB at lower addresses. The endian orientation

of a system is only evident when software performs sub-word sized accesses.

To operate an Intel

®

80200 processor in a big endian system, software running on the Intel

®

80200

processor must configure the device appropriately, and the board hosting the Intel

®

80200

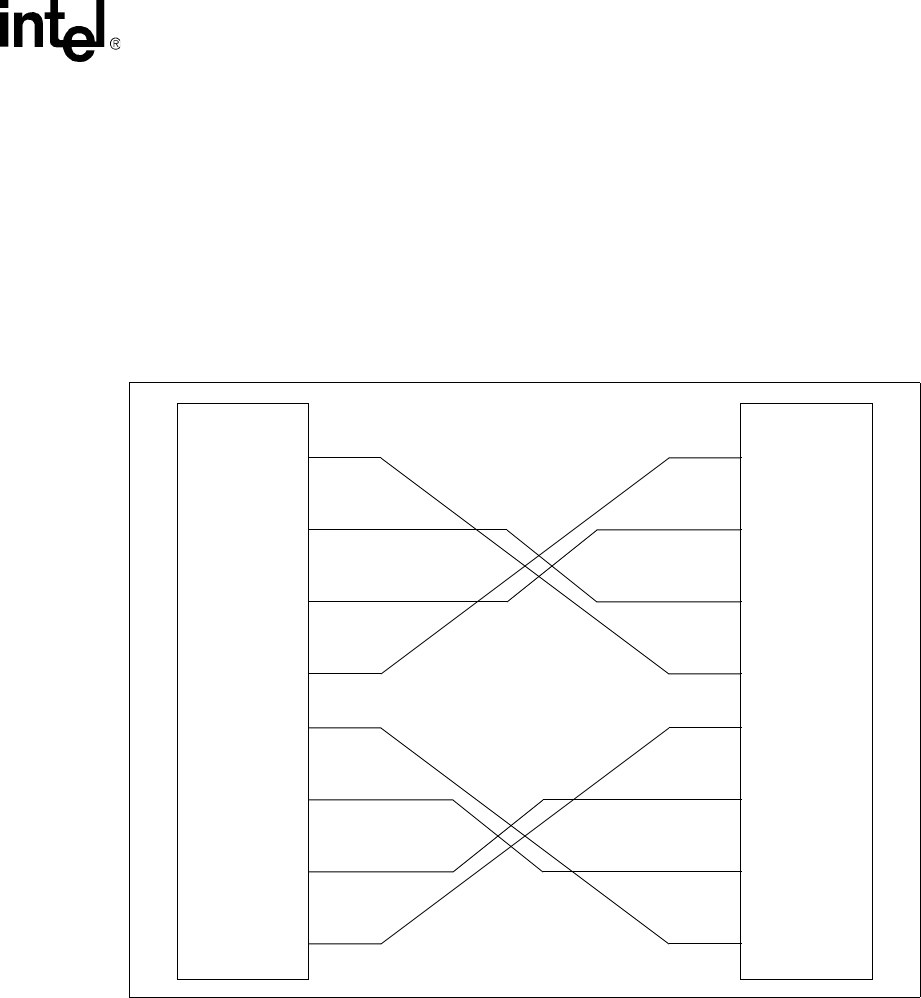

processor must swap the byte lanes in each word of the D bus. The requisite arrangement for a

64-bit bus is shown in Figure 10-3.

The lines in DCB should be wired the same for either endian configuration. Entities that create and

check ECC should always interpret the contents of memory in the system format (either big- or

little- endian).

The processor uses the Byte Enable lines (BE#) to indicate valid bytes during writes. In big-endian

systems, these lines should be swapped also. That is, bits in BE#[3:0] should be swapped, and bits

in BE#[7:4] should be swapped. This has the effect of always associating BE#[0] with D[7:0],

BE#[1] with D[15:8], and so on.

Figure 10-3. Big Endian Lane Swapping on a 64-bit Bus

D[7:0]

D[15:8]

D[23:16]

D[31:24]

D[39:32]

D[47:40]

D[55:48]

D[63:56]

Intel

®

80200

D[7:0]

D[15:8]

D[23:16]

D[31:24]

D[39:32]

D[47:40]

D[55:48]

D[63:56]

Memory

Processor