11-6 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Bus Controller

BCUCTL.TP allows software to determine if the BCU has any pending memory transactions. This

may be used to ensure that all memory operations have completed before attempting to modify

system state. For example, the code in Example 11-1 simply waits until the BCU is idle.

Of course, this sort of code should be in a cacheable region, or it may keep the BCU eternally busy

fetching the code!

If BCUCTL.EE is set, then the BCU performs ECC generation/checking as described in

Table 11-1. The other control bits (SC, SR) should only be modified while the EE bit is cleared.

To ensure correct operation, hardware waits until all pending operations are completed before

allowing the EE bit to take affect. Code similar to that shown in Example 11-2 is recommended for

enabling ECC.

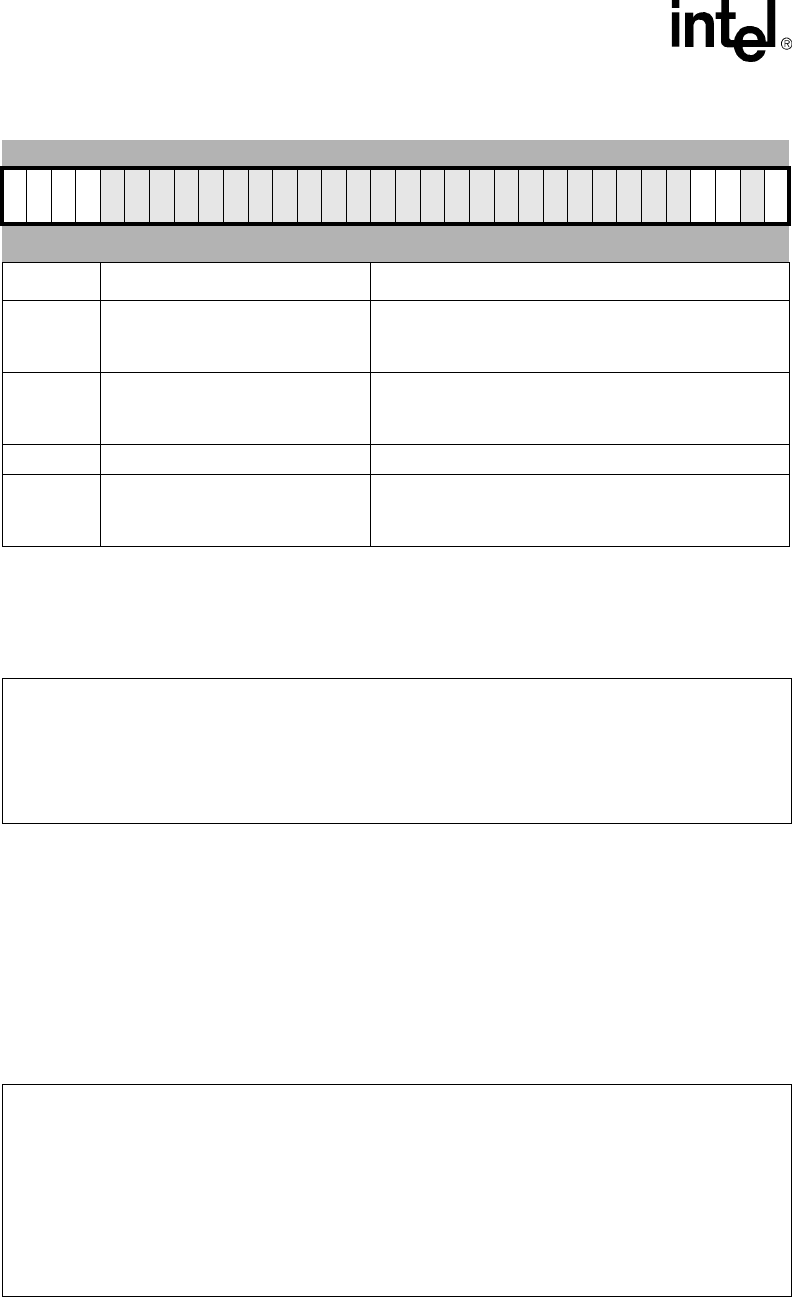

3 Read / Write

EE - ECC Enable

0 = disable ECC generation and checking

1 = enable ECC

2 Read / Write

SC - Single bit Correct Enable

0 = disable single bit error correction

1 = enable single bit error correction

1 Read-unpredictable/ Write-as-1 Reserved.

0 Read / Write

SR - Single bit Error Reporting Enable

0 = disable single bit error reporting

1 = enable single bit error reporting

Table 11-2. BCUCTL (Register 0) (Sheet 2 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

T

P

E

V

E

1

E

0

E

E

S

C

S

R

reset value: all implemented bits are 0

Bits Access Description

Example 11-1. Loop to Wait on BCU

; Wait for BCU to finish all outstanding operations

waitLoop:

MRC P13, 0, R15, C0, C1, 0 ; read BCUCTL, update condition code flags

BMI waitLoop ; try again if BCU is busy (bit 31 set)

;

; Get here when BCU is no longer busy

Example 11-2. Enabling ECC

MACRO FLUSHALL

MCR P15, 0, R0, C7, C10, 4 ; Drain buffers

ENDM

enableECC:

FLUSHALL ; Finish pending memory operations

MOV R0, #0xA ; Set bits 3 and 1

MCR P13, 0, R0, C0, C1, 0 ; Set BCUCTL -- enable ECC