Developer’s Manual March, 2003 12-5

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Performance Monitoring

12.4.1 Managing PMNC

The following are a few notes about controlling the performance monitoring mechanism:

• An interrupt is reported when a counter overflow flag is set and its associated interrupt enable

bit is set in the PMNC register. The interrupt remains asserted until software clears the

overflow flag by writing a one to the flag that is set. Note that the interrupt unit (Chapter 9,

“Interrupts”) and the CPSR must have enabled the interrupt in order for software to receive it.

• The counters continue to record events even after they overflow.

6:4 Read / Write

Interrupt Enable - used to enable/disable interrupt

reporting for each counter

Bit 6 = clock counter interrupt enable

0 = disable interrupt

1 = enable interrupt

Bit 5 = performance counter 1 interrupt enable

0 = disable interrupt

1 = enable interrupt

Bit 4 = performance counter 0 interrupt enable

0 = disable interrupt

1 = enable interrupt

3 Read / Write

Clock Counter Divider (D) -

0 = CCNT counts every processor clock cycle

1 = CCNT counts every 64

th

processor clock cycle

2 Read-unpredictable / Write

Clock Counter Reset (C) -

0 = no action

1 = reset the clock counter to ‘0x0’

1 Read-unpredictable / Write

Performance Counter Reset (P) -

0 = no action

1 = reset both performance counters to ‘0x0’

0 Read / Write

Enable (E) -

0 = all 3 counters are disabled

1 = all 3 counters are enabled

Table 12-3. Performance Monitor Control Register (CP14, register 0) (Sheet 2 of 2)

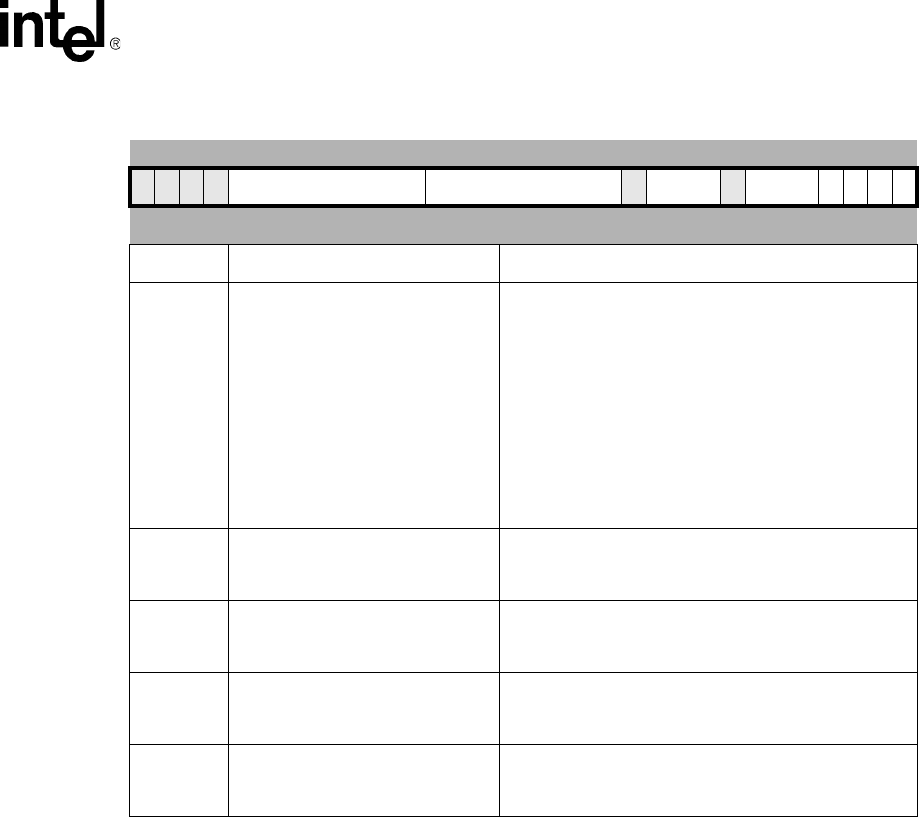

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

evtCount1 evtCount0 flag inten D C P E

reset value: E and inten are 0, others unpredictable

Bits Access Description