11-10 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Bus Controller

The BCU does not write to these ELOGx/ECARx registers unless the corresponding BCUCTL.Ex

bit is cleared, either by reset or by software.

Software can generate data with incorrect ECC values for Validation purposes. By setting a bit in

ECTST.mask to ‘1’, the corresponding bit in all generated ECCs is inverted during a write to

memory. Subsequent reads of that memory generate an ECC error.

Bit 31 in ECTST is defined as the Disable Write ECC (DWE) bit in the C-0 and D-0 steppings of

the 80200. If DWE is written as a '1', even if ECC is enabled, then the 80200 will not perform the

usual ECC actions when writing data. In other words, if DWE = '1' and a write is performed to

ECC-protected memory, the Bus Controller Unit (BCU) will not perform a RMW. The value on

the ECC bus (DCB[7:0] signals) in this case will be unpredictable but will be consistent with

whatever is being driven on D[63:0]. For example, in the case of a non-cacheable DWORD write,

D[31:0] is defined by the store instruction and D[63:32] is unpredictable. However, DCB[7:0] is

still consistent with what is driven out on D[63:0].

DWE resets to '0' and is write-only. Reads of DWE result in an unpredictable value. The actions

that the 80200 perform when reading data are unaffected by the setting of DWE.

When DWE is written, it must be done while ECC is disabled in the BCU (BCUCTL.3 = '0').

Software should only change the value of DWE once, typically at initialization/reset time.

Changing the value of DWE in other circumstances results in unpredictable behavior.

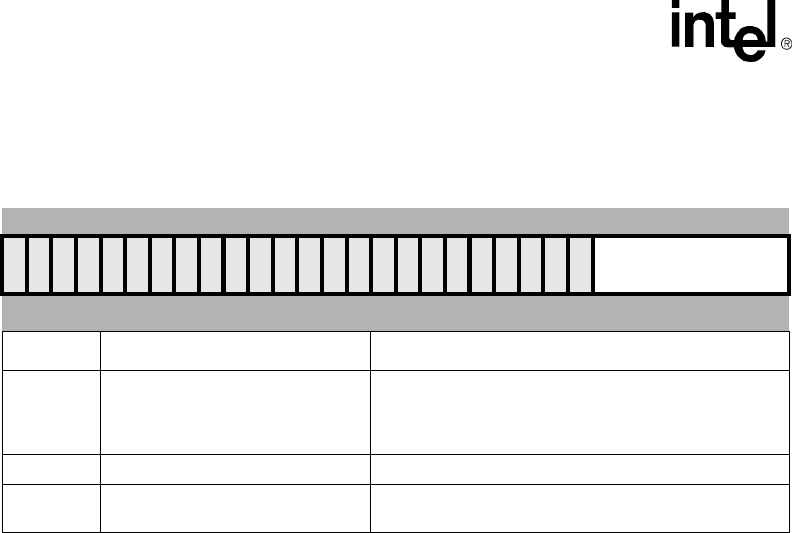

Table 11-6. ECTST (Register 8)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

D

W

E

mask

reset value: all implemented bits are 0

Bits Access Description

31 Read-unpredictable / Write

Disable Write ECC (DWE) - Disables the

Read-Modify-Write for sub-64 bit stores. If written as a

'1', even if ECC is enabled, then the 80200 will not

perform the usual ECC actions when writing data.

30:8 Read-unpredictable / Write-as-0 reserved

7:0 Read / Write

mask - When writing, the BCU exclusive-ORs this mask

with the ECC code it generates.