79

3.3 Standby Control Register (STCR)

φ

is twice as large as X0 when GCR CHC is 1, and is the cycle of PLL oscillation frequency

when CHC is 0.

[bit 01, 00] (Reserved)

These bits are reserved. The value read from this bit is undefined.

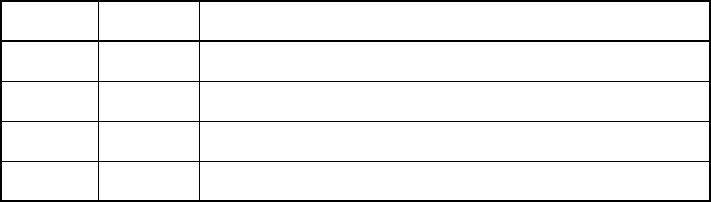

Table 3.3-1 Oscillation Stabilization Wait Time Specified by OSC1 and OSC0

OSC1 OSC0 Oscillation stabilization wait time

00

φ ×

2

15

01

φ ×

2

17

10

φ ×

2

19

11

φ ×

2

21

[Initial value]