364

CHAPTER 16 FLASH MEMORY

16.7 Execution Status of the Automatic Algorithm

This flash memory has two hardware components for performing a Write or Erase

sequence in the automatic algorithm. These components indicate the internal

operation status of flash memory and the completion of operations to external

components. One is a Ready/Busy signal and the other is a hardware sequence flag.

■

Ready/Busy Signal (RDY/BUSYX)

The flash memory uses the Ready/Busy signal in addition to the hardware sequence flag to

indicate whether the internal automatic algorithm is running. The Ready/Busy signal is

transmitted to the flash memory interface circuit, where it can be read via the "RDY" bit of the

flash memory status register. An interrupt signal can also be generated for the CPU at the

rising edge of this Ready/Busy signal (see Section 16.1, "Outline of Flash Memory").

When the value of the "RDY" bit is "0", the flash memory is executing a write or erase operation,

where new Write and Erase commands are not accepted.

When the value of the "RDY" bit is "1", the flash memory is in read/write or erase operation wait

state.

■

Hardware Sequence Flag

For obtaining the hardware sequence flag as data, read an arbitrary address (an odd address in

byte access) from flash memory when the automatic algorithm is executed. The data contains

five validity bits which indicate the status of the automatic algorithm.

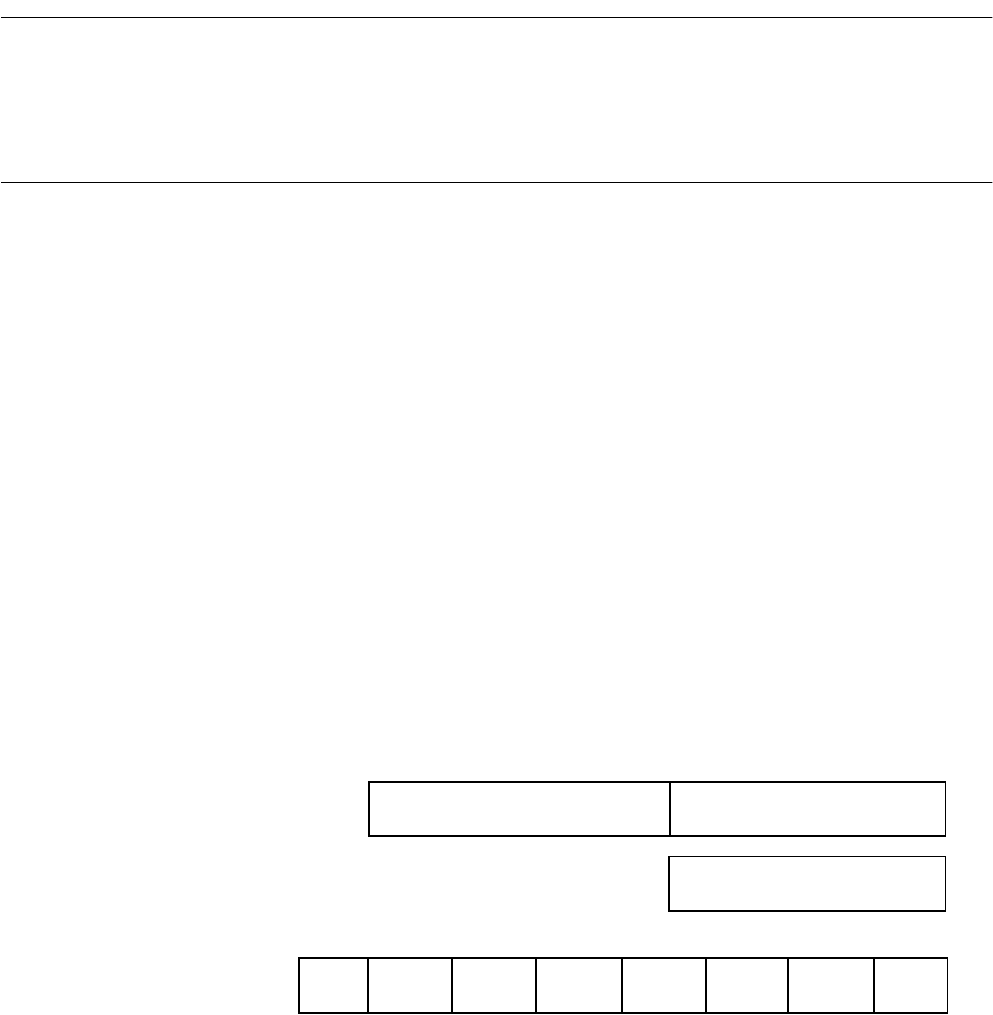

Figure 16.7-1 shows the structure of the hardware sequence flag.

Reading in units of words is inhibited.

Figure 16.7-1 Structure of the Hardware Sequence Flag

The hardware sequence flag becomes invalid in FR-CPU ROM mode. Always use FR-CPU

programming mode and write only in half-words or bytes.

15

80

7

0

SETIMR TOGGL2

DPOLL TOGGLE TLOVER

7

7

3

456

0

1

2

bit

During half-word read

Hardware sequence flag

During byte read (from odd address only)

Hardware sequence flag

(In half-word and byte access)

Undefined

UndefinedUndefined

(Undefined)