107

3.14 Clock Doubler Function

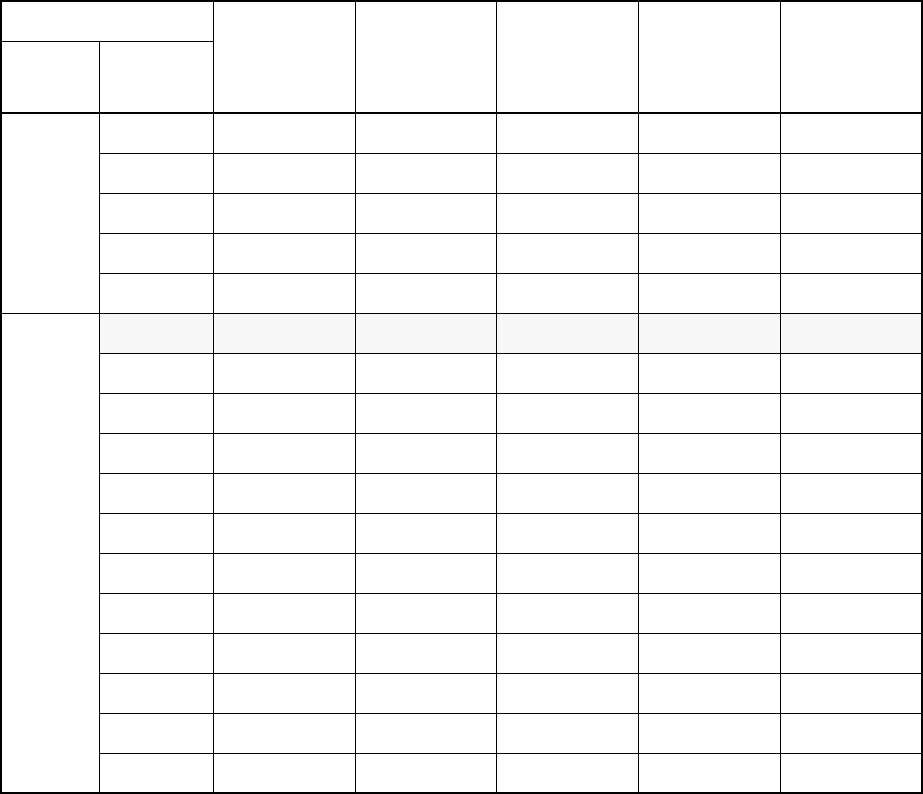

register. (Table 3.14.1 shows an example for the case that a 12.5 MHz oscillation is used.)

*1: Fixed to 1/1 regardless of settings

*2: To disable the clock doubler function, switch the clock to the divide-by-two clock in advance.

*3: When the PLL oscillation frequency is changed, the clock must be switched to the divide-by-

two clock.

Table 3.14-1 Operating Frequency Combinations Depending on whether the Clock Doubler Function is

Enabled or Disabled

GCR PLL

oscillation

frequency

(MHz)

Clock

doubler

Internal

operating

frequency

(MHz)

External

bus

frequency

(MHz)

Remarks

CHC Gear

Divide-

by-two

1/1 OFF 6.25 6.25

1/2 OFF 3.12 3.12

1/4 OFF 1.56 1.56

1/8 OFF 0.78 0.78 Initial value

(*1) ON 6.25 3.12

PLL *

3

- 50.0 OFF 50.0 50.0 Inhibited

1/1 25.0 OFF 25.0 25.0

1/2 25.0 OFF 12.5 12.5

1/4 25.0 OFF 6.25 6.25

1/8 25.0 OFF 3.12 3.12

1/1 12.5 OFF 12.5 12.5

1/2 12.5 OFF 6.25 6.25

1/4 12.5 OFF 3.12 3.12

1/8 12.5 OFF 1.56 1.56

*1 50.0 ON 50.0 25.0 *2

*1 25.0 ON 25.0 12.5

*1 12.5 ON 12.5 6.25