273

11.2 Control Status Register (ADCS)

<Note>

A/D conversion that is started in continuous conversion mode or convert-and-stop mode

continues until the BUSY bit stops it.

Writing "0" to the BUSY bit stops A/D conversion.

"No restart is enabled" in single conversion, continuous conversion, or convert-and-stop mode

applies to all start causes including the timer, external trigger signal, and software.

[bit 5, 4, 3] ANS2, ANS1, ANS0 (ANalog Start channel set)

These bits are used to set the A/D conversion start channel.

When started, the A/D converter begins A/D conversion with the channel selected by these

bits.

When read, these bits indicates the channel over which A/D conversion is being performed.

When read while the A/D converter is stopped in convert-and-stop mode, the bits indicate

the channel over which A/D conversion has been previously completed.

These bits are initialized to "000" when the register is reset.

[bit2, 1, 0] ANE2, ANE1, ANE0 (ANalog End channel set)

These bits are used to set the A/D conversion end channel.

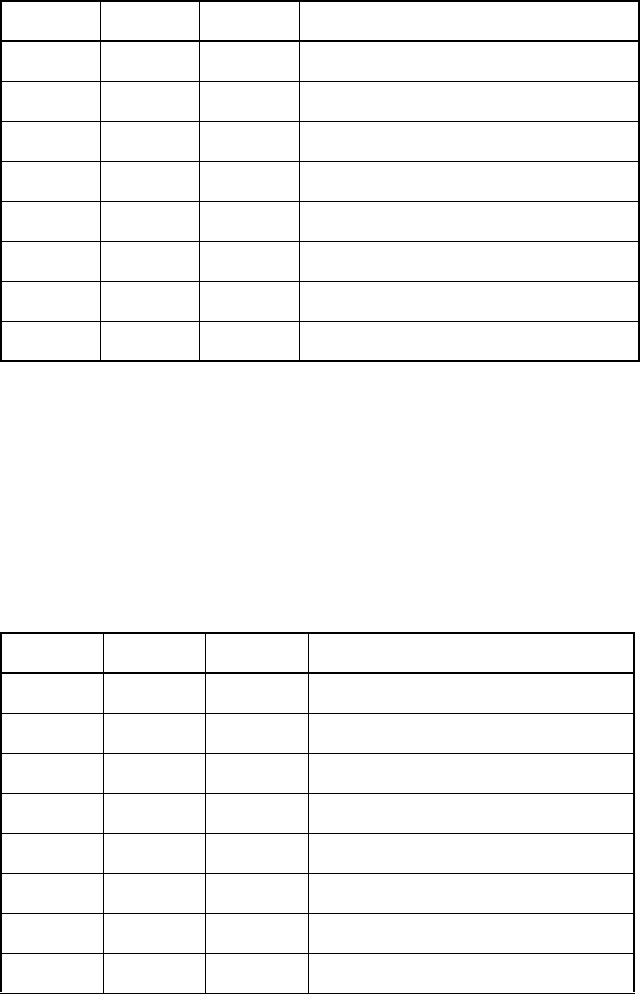

Table 11.2-3 Setting the A/D Conversion Start Channel

ANS2 ANS1 ANS0 Start channel

000AN0

001AN1

010AN2

011AN3

100Reserved

101Reserved

110Reserved

111Reserved

Table 11.2-4 Setting the A/D Conversion End Channel

ANE2 ANE1 ANE0 End channel

000AN0

001AN1

010AN2

011AN3

100Reserved

101Reserved

110Reserved

111Reserved