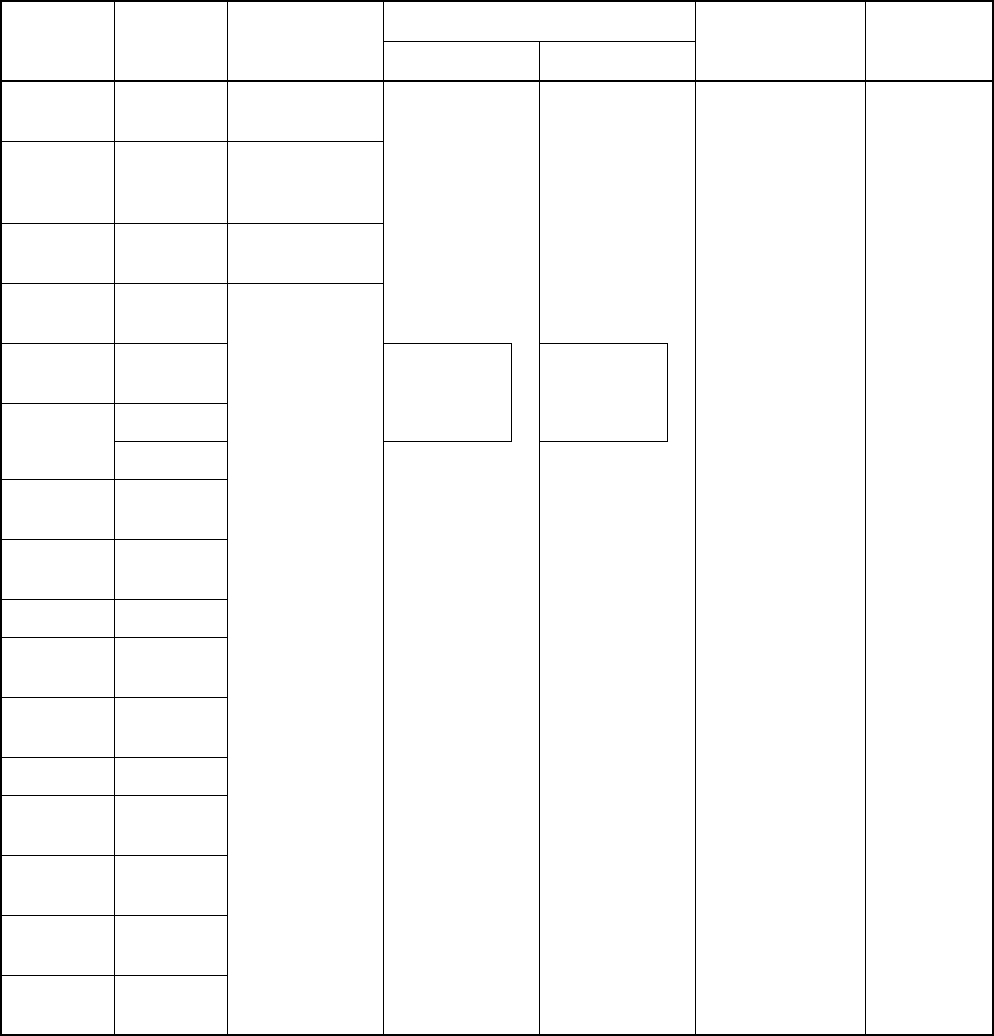

394

APPENDIX C Pin Status for Each CPU Status

P: when a general-purpose port is specified, F: when the specified function is selected

PB5 DREQ2 Previous status

retained

Output Hi-Z/

All pins

Input

possible

PB6 DACK2 P: Previous

status retained

F: DACK output

PB7 Port Previous status

retained

AN0 to

AN3

AN0-3 Previous status

retained

PE0 to

PE2

INT0-INT2 Input

possible

Input

possible

PE3 INT3

SC2

PE4 to

PE5

DREQ0-

DREQ1

PE6 to

PE7

DACK0-

DACK1

PF0 SI0, TRG0

PF1 SO0,

TRG1

PF2 SC0,

OCPA3

PF3 SI1, TRG2

PF4 SO1,

TRG3

PF5 SI2,

OCPA1

PF6 SO2,

OCPA2

PF7 OCPA0,

ATGX

Table C-5 Pin Status in Single Chip Mode (Continued)

Pin name Function During sleep During stop — Reset time

HIZX=0

HIZX=1