124

CHAPTER 4 BUS INTERFACE

4.7 Area Mode Register 32 (AMD32)

Area mode register 32 (AMD32) controls the operation mode of chip select area 2 (area

specified by ASR2 and AMR2) and chip select area 3 (area specified by ASR3 and

AMR3).

These areas are accessed only via the usual bus and do not allow the use of special

DRAM interfaces.

The BW1 and BW0 bits can control the same bus width as those of areas 2 and 3. The

number of automatic wait cycles can be specified for each area.

■

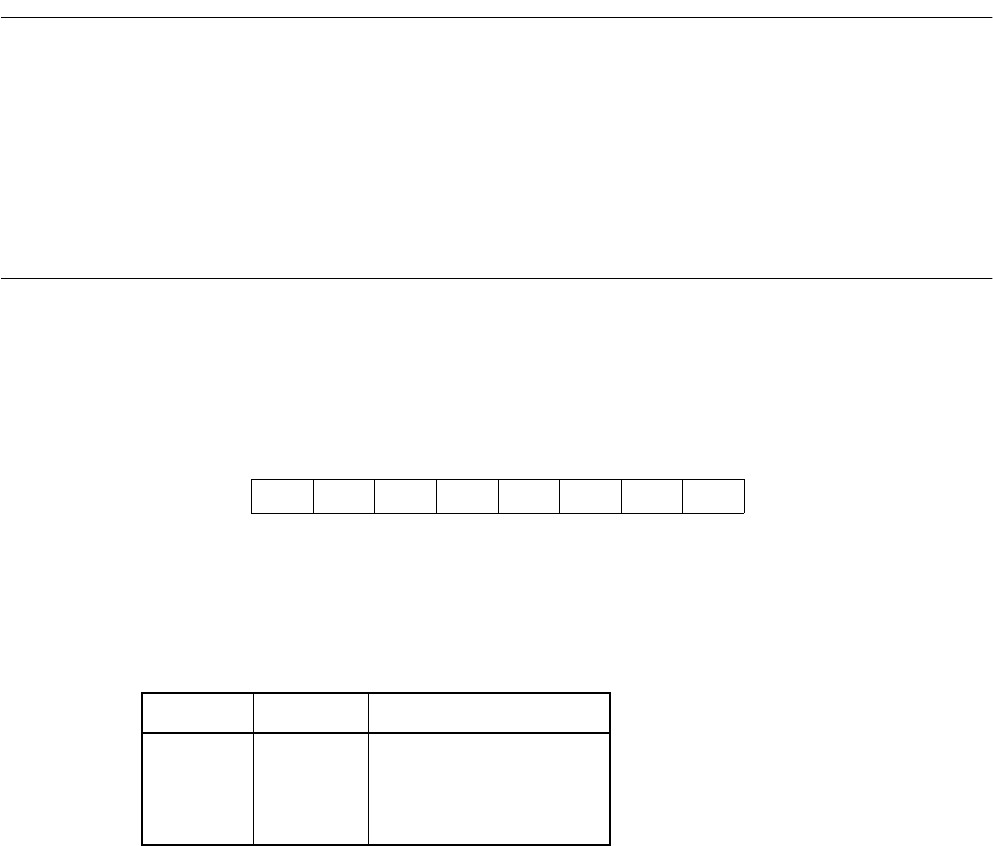

Configuration of Area Mode Register 32 (AMD32)

Area mode register 32 (AMD32) is configured as follows:

■

Bit Functions of Area Mode Register 32 (AMD32)

[bit 7 and 6] BW1 and 0 (Bus Width bit)

BW1 and BW0 specify the bus width of area 2 or area 3.

[bit 5 to 3] WT32 to 30 (Wait Cycle bit)

WT32 to WT30 specify the number of wait cycles to be inserted automatically when area 3 is

accessed via memory.

The operation of the bits is similar to WTC2 to WTC0 of AMD0.

The bits are reset to "000", and the number of wait cycles to be inserted becomes "0".

[bit 2 to 0] WT 22 to 20 (Wait Cycle bit)

WT22 to WT20 specify the number of wait cycles to be inserted automatically when area 2 is

accessed via memory.

The operation of the bits is similar to WTC2 to WTC0 of AMD0.

The bits are reset to "000", and the number of wait cycles to be inserted becomes "0".

76543210

AMD32

0622

H

BW1 BW0 WT32 WT31 WT30 WT22 WT21 WT20 00000000 R/W

Address: 0000

Initial value Access

BW1 BW0 Bus width

0

0

1

1

0

1

0

1

8 bits

16 bits

Setting disabled

Reserved