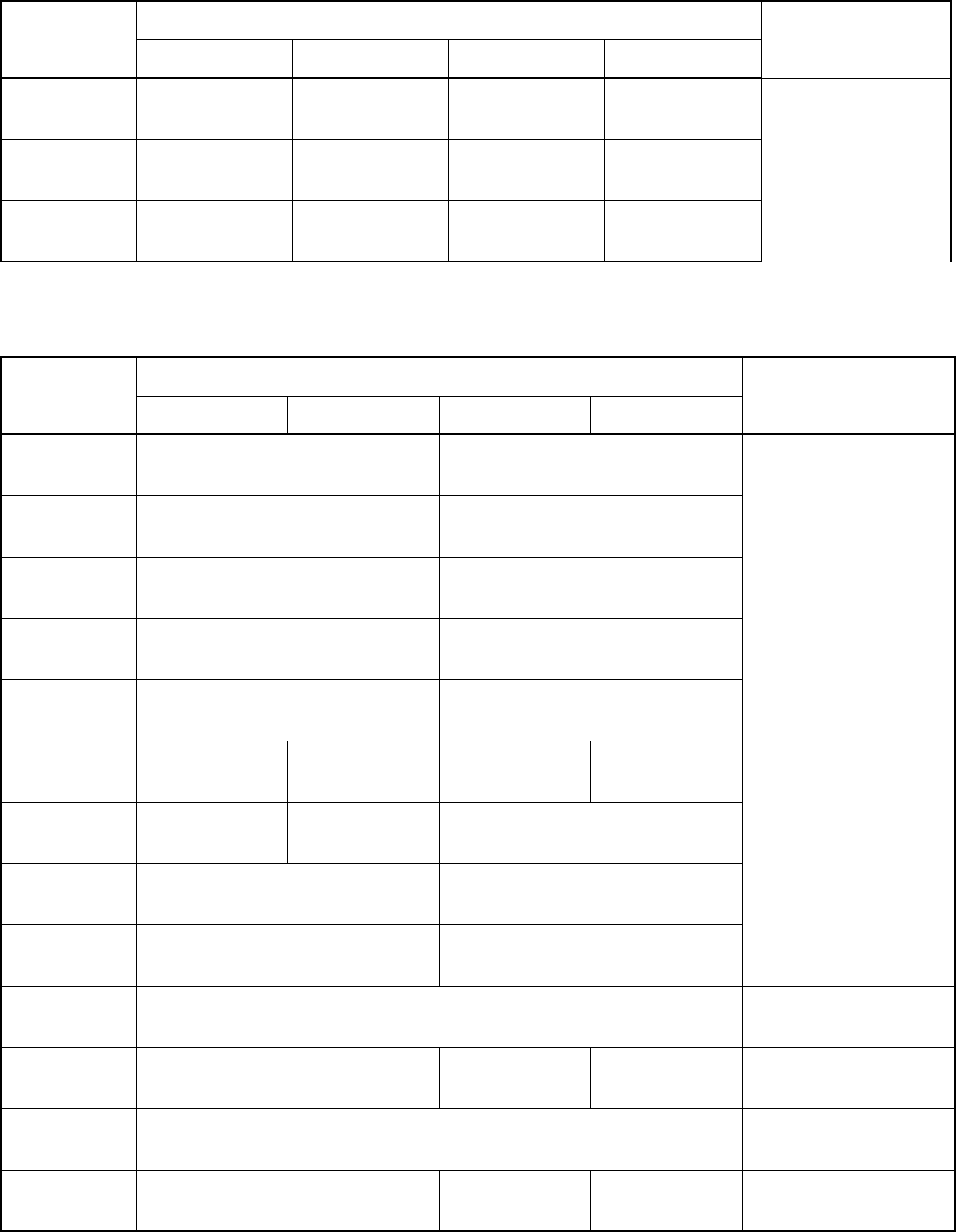

377

APPENDIX A I/O Maps

000600

H

DDR3 [W]

00000000

DDR2 [W]

00000000

- - Data direction

register

000604

H

DDR7 [W]

-------0

DDR6 [W]

00000000

DDR5 [W]

00000000

DDR4 [W]

00000000

000608

H

DDRB [W]

00000000

DDRA [W]

-0000000

- DDR8 [W]

--000000

Table A-5 I/O Map (5/6)

Address Register Internal resource

+0 +1 +2 +3

Table A-6 I/O Map

Address Register Internal source

+0 +1 +2 +3

00060C

H

ASR1 [W]

00000000 00000001

AMR1 [W]

00000000 00000000

External bus interface

000610

H

ASR2 [W]

00000000 00000010

AMR2 [W]

00000000 00000000

000614

H

ASR3 [W]

00000000 00000011

AMR3 [W]

00000000 00000000

000618

H

ASR4 [W]

00000000 00000100

AMR4 [W]

00000000 00000000

00061C

H

ASR5 [W]

00000000 00000101

AMR5 [W]

00000000 00000000

000620

H

AMD0 [R/W]

---XX111

AMD1 [R/W]

0--00000

AMD32 [R/W]

00000000

AMD4 [R/W]

0--00000

000624

H

AMD5 [R/W]

0--00000

DSCR [W]

00000000

RFCR [R/W]

--XXXXXX 00---000

000628

H

EPCR0 [W]

----1100 -1111111

EPCR0 [W]

-------1 11111111

00062C

H

DMCR4 [R/W]

00000000 0000000-

DMCR5 [R/W]

00000000 0000000-

000630

H

to

0007BC

H

- Reserved

0007C0

H

FSTR [R/W]

000XXXX0

- - Flash memory

0007C4

H

to

0007F8

H

- Reserved

0007FC

H

- LER [W]

-----000

MODR [W]

XXXXXXXX

Little endian register

mode register