253

10.5 Serial Status Register (SSR)

10.5 Serial Status Register (SSR)

The serial status register (SSR) consists of flags that show the UART operating status.

■

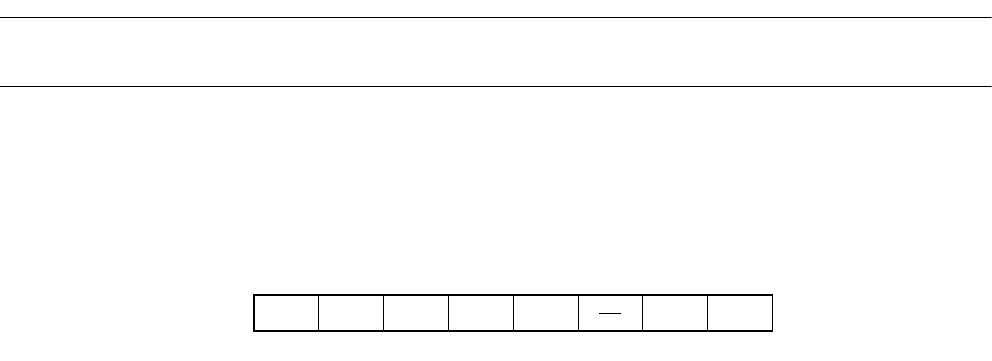

Configuration of Serial Status Register (SSR)

The configuration of the serial status register (SSR) is shown below:

■

Bit Function of Serial Status Register (SSR)

[bit 7] PE (Parity Error)

This bit is an interrupt request flag that is set when a parity error is detected for received

data.

To clear the flag once it is set, set the REC bit (bit 10) of the SCR register to "0".

When this bit is set, SIDR data is invalidated.

0: No parity error is present. (Initial value)

1: A parity error is present.

[bit 6] ORE (Over Run Error)

This bit is an interrupt request flag that is set when an overrun is detected for received data.

To clear the flag once it is set, set the REC bit of the SCR register to "0".

When this bit is set, SIDR data is invalidated.

0: No overrun is present. (Initial value)

1: An overrun is present.

[bit 5] FRE (FRaming Error)

This bit is an interrupt request flag that is set when a framing error is detected for received

data.

To clear the flag once it is set, set the REC bit of the SCR register to "0".

When this bit is set, SIDR data is invalidated.

0: No framing error is present. (Initial value)

1: A framing error is present.

76543210

SSR 00001C

H

Address:000020

H

PE ORE FRE RDRF TDRE RIE TIE 00001-00

B

000024

H

RRRRR R/WR/W

Initial value