193

4.17 Bus Timing

4.17.21 External Bus Request

This section provides external bus request timing charts.

■

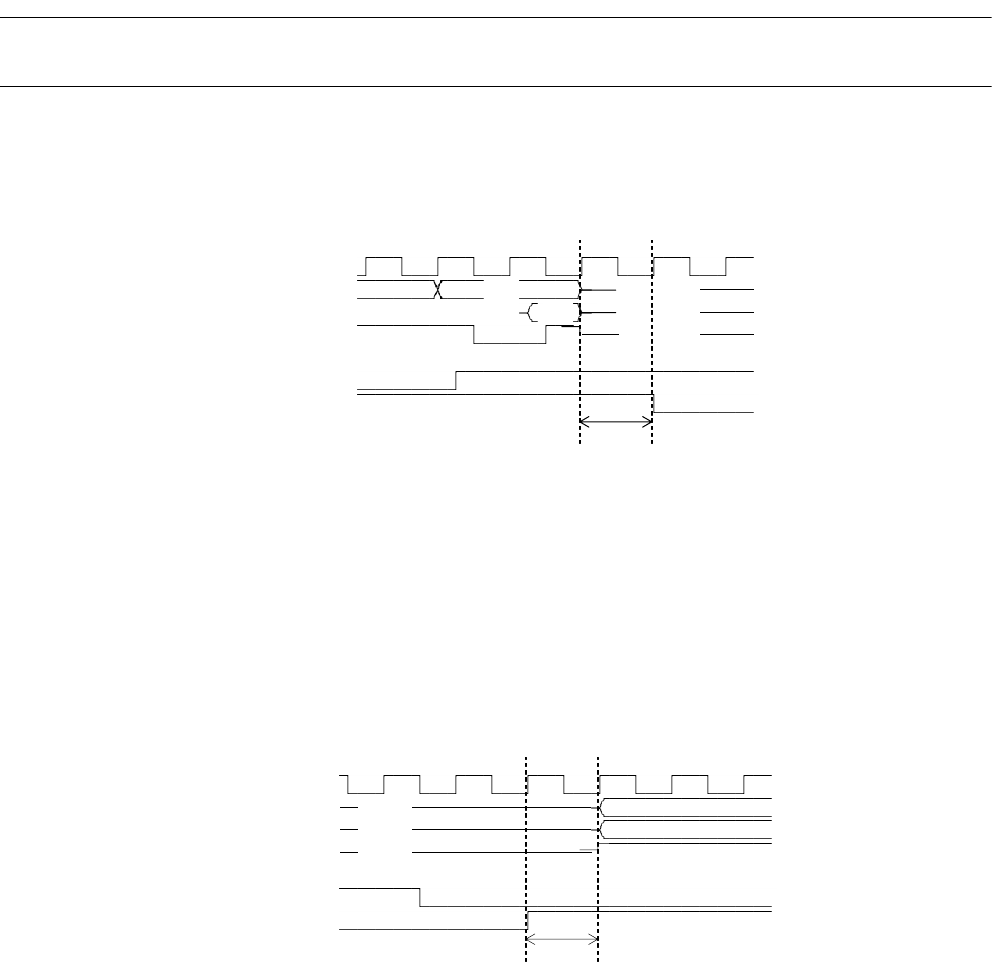

Bus Control Release

Figure 4.17-38 Example of Bus Control Release Timing Chart

[Explanation of operation]

• When performing bus arbitration by BRQ and BGRNTX, set the BRE bit of EPCR0 to "1".

• When releasing bus control, set the corresponding pins to High-Z and assert BGRNTX one

cycle later.

■

Bus Control Acquisition

Figure 4.17-39 Example of Bus Control Acquisition Timing

[Explanation of operation]

• When performing bus arbitration by BRQ and BGRNTX, set the BRE bit of EPCR0 to "1".

• When acquiring bus control, negate BGRNTX and activate each pin one clock later.

CLK

A24-00 #0:1 high

Z

D31-16 #0:1 high Z

RDX high Z

BRQ

BGRNTX

1 cycle

CLK

A24-00 high Z

D31-16 high Z

RDX high Z

BRQ

BGRNTX

1 cycle