180

CHAPTER 4 BUS INTERFACE

❍

Bus width: 16 bits, access: bytes

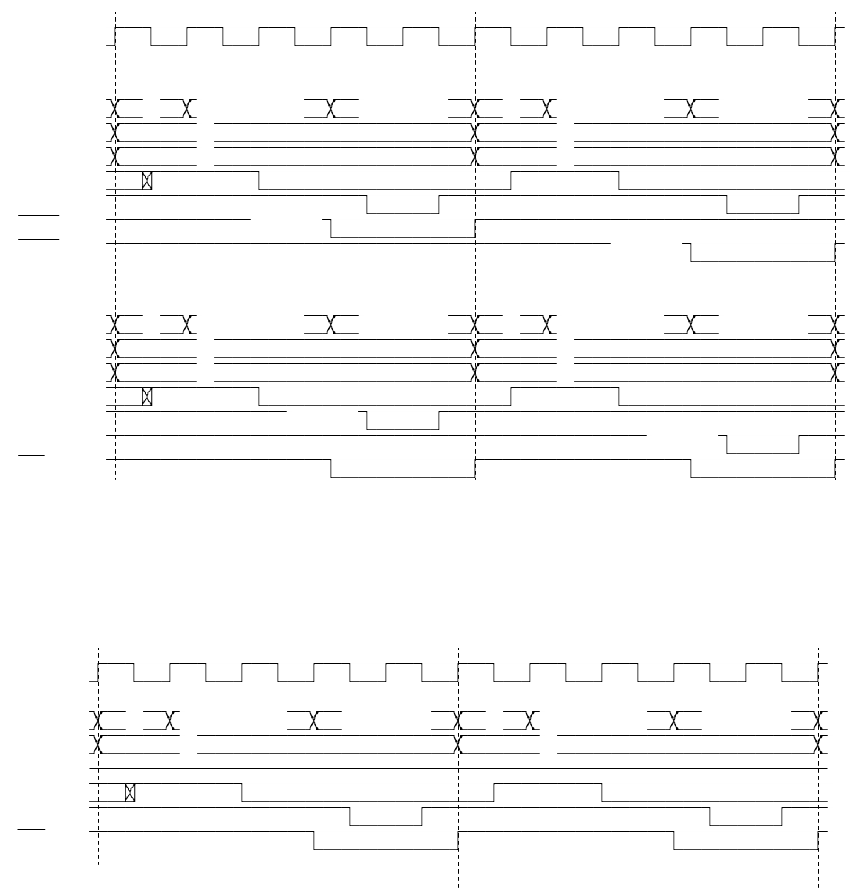

Figure 4.17-22 Example 2 of Usual DRAM Write Cycle Timing Chart

❍

Bus width: 8 bits, access: half-words

Figure 4.17-23 Example 3 of Usual DRAM Write Cycle Timing Chart

Q1 Q2 Q3 Q4 Q5 Q1 Q2 Q3 Q4 Q5

CLK

1)1CAS/2WE

A24-00

X #0 row.adr. #0 col.adr X #1 row.adr. #1 col.adr

D31-24 #0 X

D23-16 X #1

RAS

CAS

WEL

WEH

2)2CAS/1WE

A24-00

X #0 row.adr. #0 col.adr X #1 row.adr. #1 col.adr

D31-24 #0 #1

D23-16 X #1

RAS

CASL

CASH

WE

Upper address side

Lower address side

Upper address side

Lower address side

Q1 Q2 Q3 Q4 Q5 Q1 Q2 Q3 Q4 Q5

CLK

A24-00 X #0 row.adr. #0 col.adr X #1 row.adr. #1 col.adr

D31-24 #0 X

D23-16

RAS

CAS

WE