312

CHAPTER 14 PWM TIMER

■

Bit Functions of General Control Register 1 (GCN1)

[bits 15-12] TSEL 33-30: ch3 trigger input select bits

[bits 11-8] TSEL 23-20: ch2 trigger input select bits

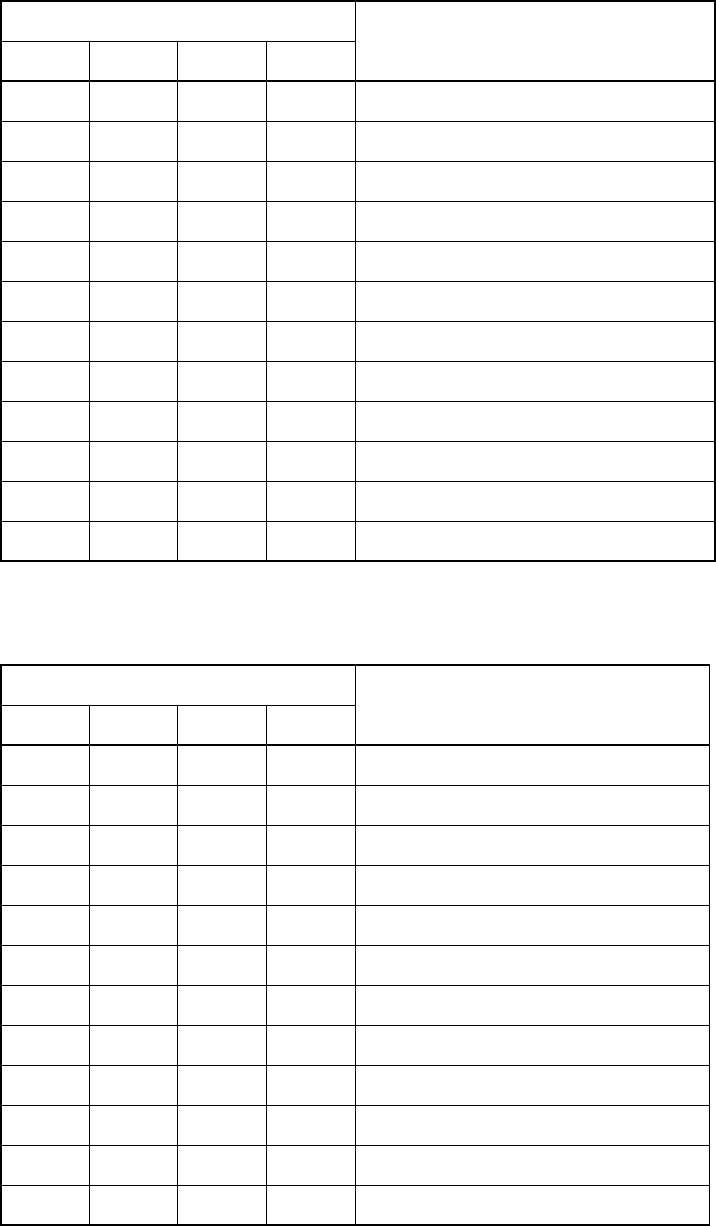

Table 14.7-1 Selection of Ch3 Trigger Input

TSEL33-30 ch3 trigger input

15 14 13 12

0 0 0 0 GCN2 EN0 bit

0 0 0 1 GCN2 EN1 bit

0 0 1 0 GCN2 EN2 bit (Initial value)

0 0 1 1 GCN2 EN3 bit

0 1 0 0 16-bit reload timer channel 0

0 1 0 1 16-bit reload timer channel 1

011XReserved

1000External TRG0

1001External TRG1

1010External TRG2

1011External TRG3

11XXReserved

Table 14.7-2 Selection of Ch2 Trigger Input

TSEL23-20 ch2 trigger input

11 10 9 8

0 0 0 0 GCN2 EN0 bit

0 0 0 1 GCN2 EN1 bit (Initial value)

0 0 1 0 GCN2 EN2 bit

0 0 1 1 GCN2 EN3 bit

0 1 0 0 16-bit reload timer channel 0

0 1 0 1 16-bit reload timer channel 1

011X Reserved

1000External TRG0

1001 External TRG1

1010External TRG2

1011External TRG3

11XXReserved